Hi all

Would you mind if we ask DRV8412?

We would like to confirm /FAULT behavior in case of overcurrent shutdown.

There is the description on Table1.

We assume that it depends on M1~M3 settings.

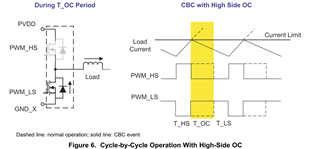

In case of cycle-by-cycle current limit(M1=M2=M3=0)

->Fault pin is asserted during PWM_HS's low(yellow blocks).

In case of OC latching shutdown(M1=1, M2=M3=0)

->Fault pin is asserted until reset or restart(power on and off toggling).

Is our recognition correct?

Kind regards,

Hirotaka Matsumoto

-

Ask a related question

What is a related question?A related question is a question created from another question. When the related question is created, it will be automatically linked to the original question.