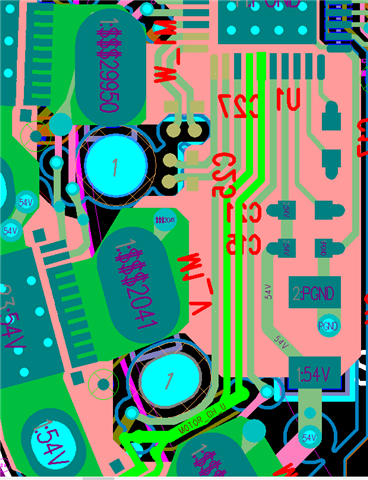

Other Parts Discussed in Thread: CSD88599Q5DC

Hi all:

Our products use DRV8323 to drive PMSM.We have often encountered 8323 damage recently,All the damage is gate drive fault on high-side MOSFET

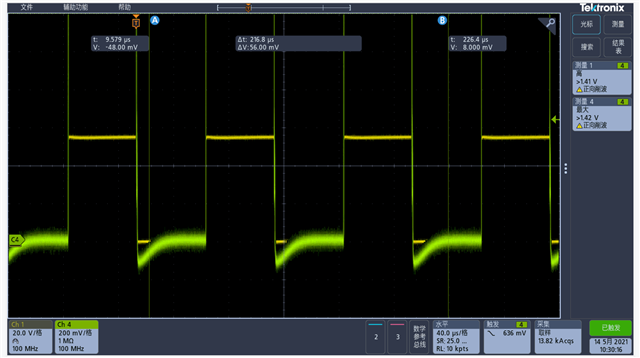

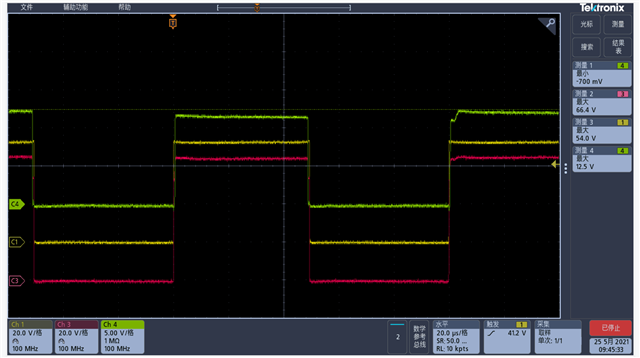

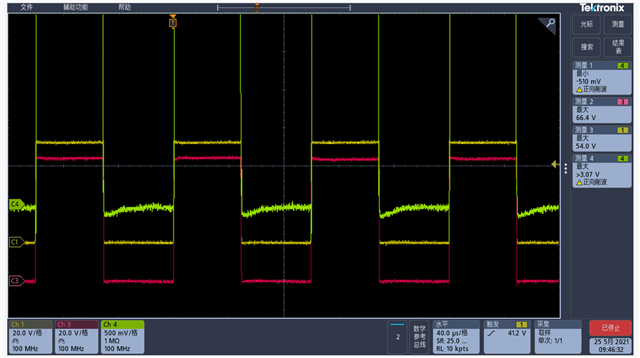

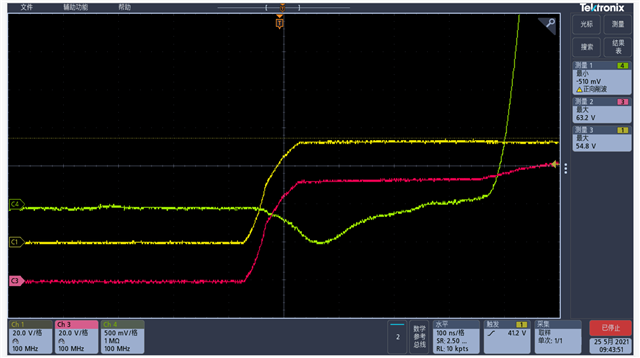

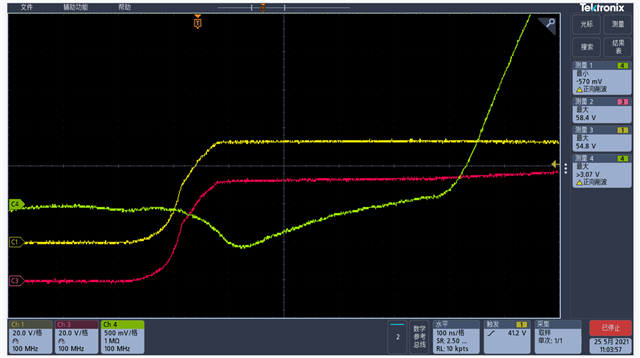

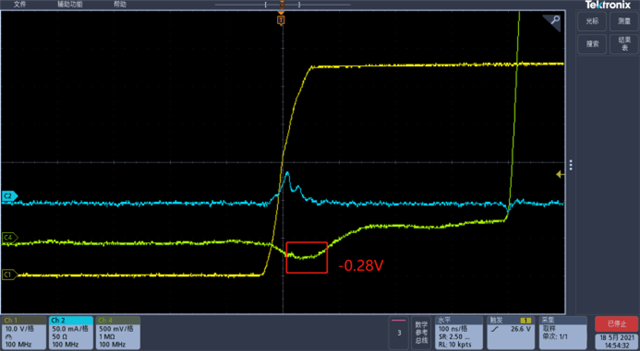

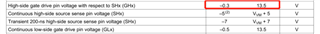

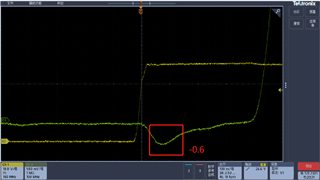

All the damaged devices are DRV8323, not MOSFET. We did some tests and found that the negative voltage of High-side gate drive pin voltage with respect to SHx(GHx) is out of specification,as shown below

Noted:

CH1: Continuous high-side source sense pin voltage (SHx)

CH4:High-side gate drive pin voltage with respect to SHx (GHx)

We found that this negative voltage appears very frequently when the motor has current, which may be the cause of the damage of DRV8323

We use 3x PWM mode ,We tried changing the IDRIVE and dead time, but it didn’t work

Have you ever encountered a similar situation? Do you have any suggestions for this situation?

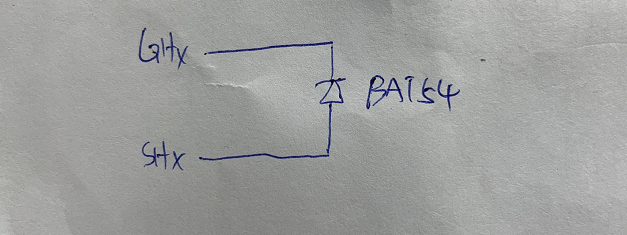

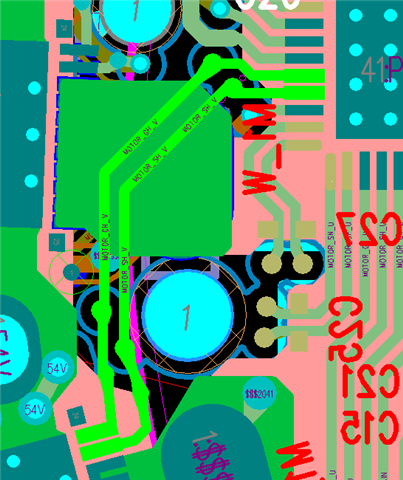

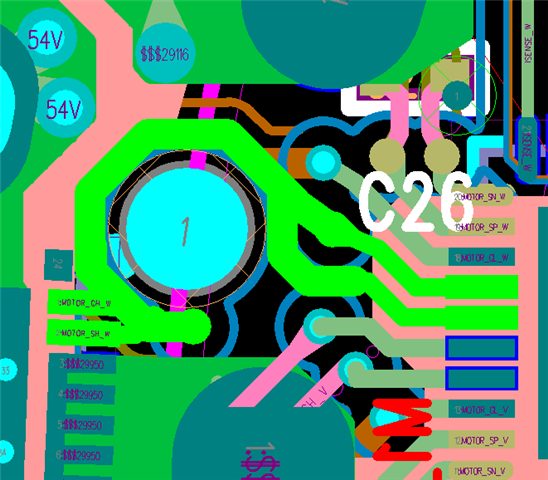

Attach our schematic

Looking forward to your reply

Thanks

ZX