Other Parts Discussed in Thread: DRV8320, DRV832X, BOOSTXL-DRV8320RS, LAUNCHXL-F280025C,

Hi

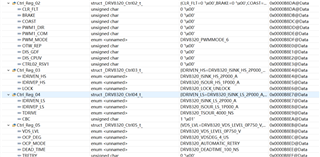

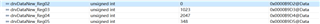

1.Read register is OK, if not write register,the registers read out are the default values when they are not set. The register values are as follows:

To see which side caused it, I added two breakpoints (the blue arrow).

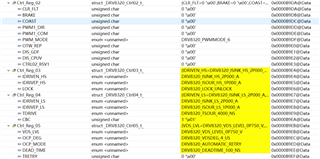

3.Next, continue to run the code. As expected, the read register value should also be the register value in step 2, but the actual register value is as follows:

It can be seen that almost all the register values have changed. I don't know why?

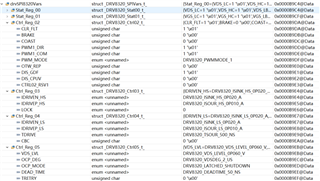

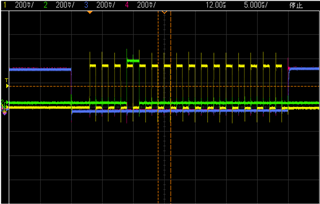

4. So I was in drv8320_ writeData(ETV_ Four variables are added to handle, & drvspi8320vars) to record whether the parameters written to 2, 3, 4 and 5 register values are correct or not. After running the code, it is shown in the figure below,

The variable value is consistent with that in step 2, which means drv8320_ The entry parameters of writespi (handle, drvregaddr, drvdatanew) are correct,

But there will be a problem after write. I don't know where the problem is?

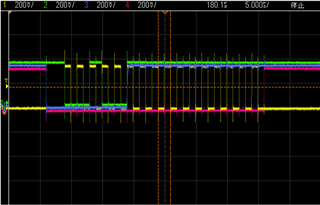

The waveforms written to registers 2, 3, 4 and 5 are as follows

Thanks!