Hi team

I would like to ask some questions about the process of how could we successfully detect the stall condition?

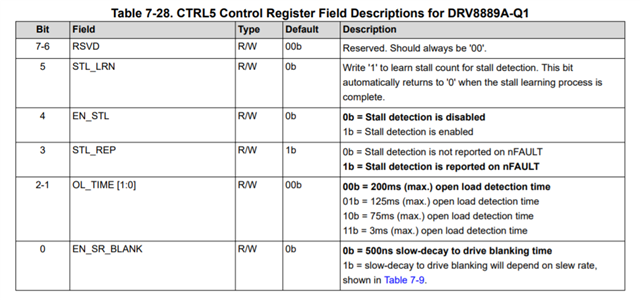

1. I know we should configure the CTRL5 register bit[5] to 1 and bit[4] to 1 to let the DRV8889Q1 first to finish the stall learning, after that we see the bit[5] return to 0b and we could see the STL_LRN_OK goes high so it means the stall learning is OK right?

2. After that we could start the stall detection and see the SPI diagnose register DIAG_2 bit[3] to check whether it succeed in stall detection? What about the configuration of CTRL 5 bit[3]? Both bit[3] to 0 or 1 could we read the DIAG_2 bit[3] to check whether the stall detection start?

3. When the device recognizes the stall status and how much stall current threshold/requirement does the device recognize it will enter the stall status?