Other Parts Discussed in Thread: DRV8353

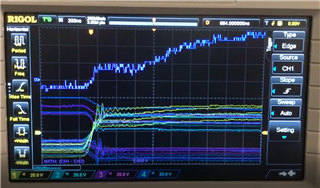

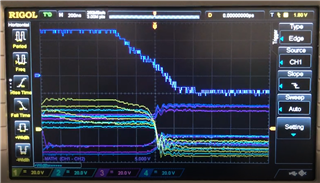

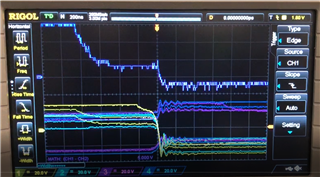

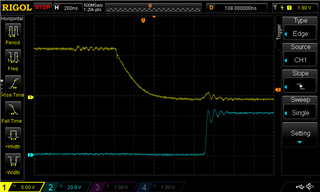

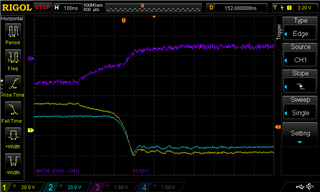

I am running the DRV8353 and measuring the gate-source difference. There is a significant variation in the rise time that shouldn't exist. Some examples are below (Blue is gate, yellow is source, purple is gate -source):

This is over the same MOSFET and constant load so it would be expected the wave forms to be very similar.

I have tried this with an IDRIVE of 300/600mA and 450/900mA and the variation occurs in both.

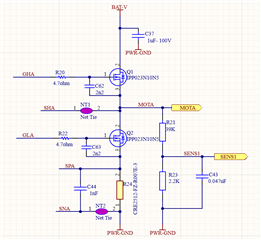

The schematic for a single phase is as below:

Is there a reason that this variation would occur and how could I eliminate it? The hardware chip is being used and is configured to be 6x PWM, 10V/V gain and 0.2V Overcurrent trip voltage.

Thanks,

Oliver