Other Parts Discussed in Thread: DRV8301, DRV8353

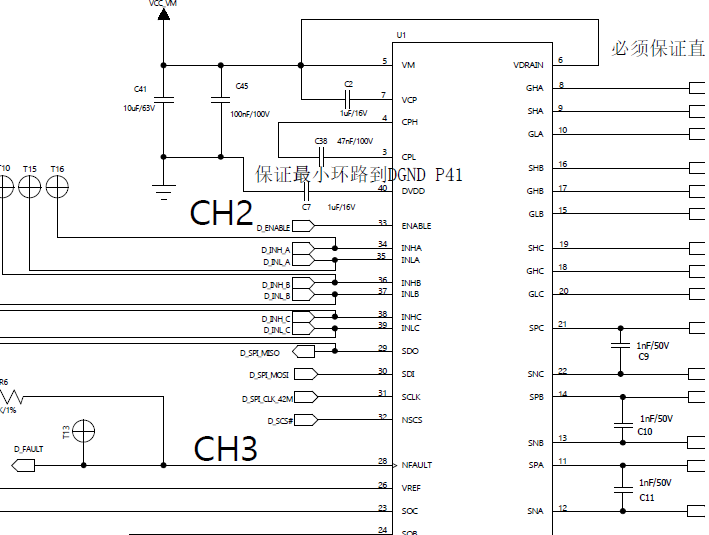

As shown in the following figure, VCC _VM is DC24V, NFAULT pull-up resistor 2.2 k.

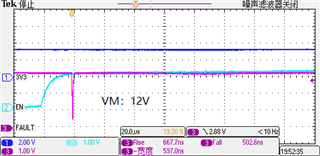

When EN pin is enabled (pulled high), the NFAULT pin generates a negative pulse. And then the MCU interrupt was caused, internal data was read through SPI, and there was no specific fault bit, as shown in Figure 2 for the test graph.

The customer would like to know what is the possible reason for that.

Thanks!

Best Regards,

Cherry Zhou