Dear expert,

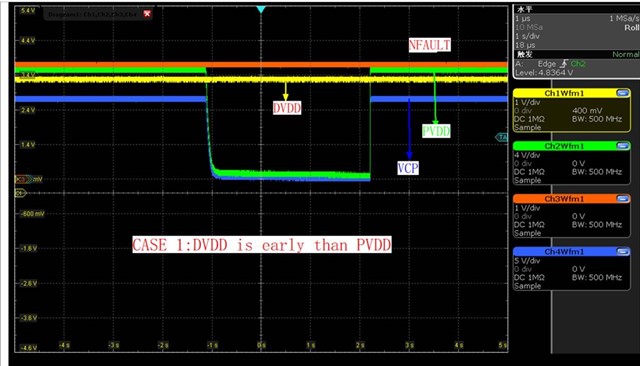

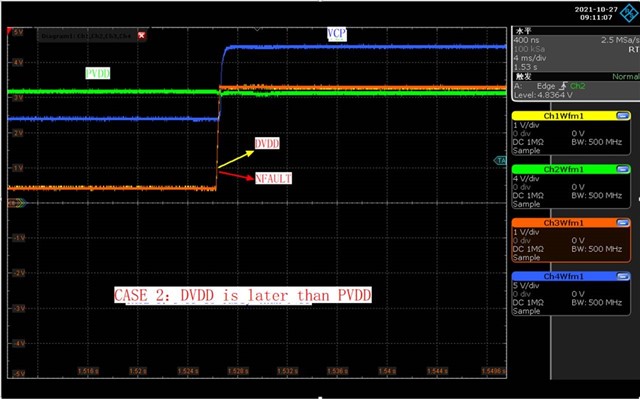

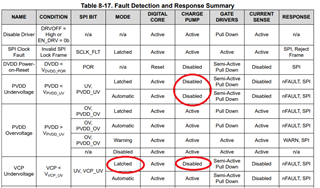

During debug, We found there is no output for VCP if DVDD power up before PVDD. And there is normal 20V output at VCP if PVDD power up before DVDD.

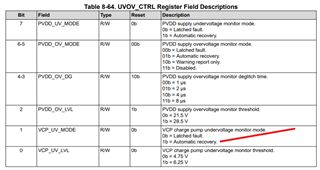

Is it as expected? I cannot find this requirement in the datasheet.

If no, could you guide us how to fix it?

Great thanks