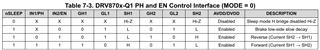

We plan to control our actuator using MODE '0' first

and use 2 mode(Reverse, Forward) only

so, IN2 is fixed as '1' and IN1 will receive 80[khz] PWM frequency to control actuator

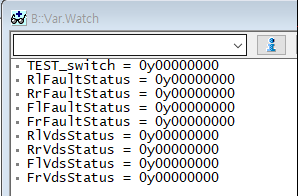

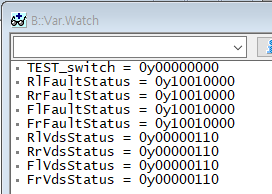

but in this phase If I change IN1 frequency, then VDS register bit act differently in the same voltage input like below

-80[khz] PWM input (voltage condition 16[v], actuator current 1.5[A/channel], there are 4 channel)

- 30[khz] PWM input

VDS register bit is set sensitively if receive lower PWM input even if in same voltage and same actuator current environment

There's only one different thing. PWM frequency.

We are planning to design fail safe concept by using this register information, so we have to know the root reason thoroughly

Can I know the reason why?