Hi Team,

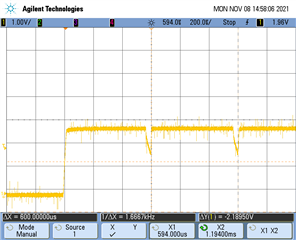

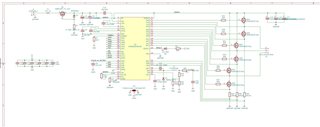

My prototype board use DRV8353RS and worked. Board is powered from laboratory supply 25V. Now consumption increased probably after reset to more than 130mA and DRV heats. VGS Status2=00000040 (VCP or VLGS undervoltage). When Enable is low consumption is OK. I tried to disconnect GHx and GLx and nothing changed. Is DRV destroyed and why? I only have one DRV left now and I'm afraid to use it until I find out the causes of the destruction. The same situation occurred a month ago.

Thank you

Pavel

Board uses 1xPWM with HALL sensor.

Startup sequence:

During the reset is Enable held down by external resistor 10kOhm.

Program set Enable, INHx and INLx to LOW.

Than On INLA connect PWM.

Set enable to HIGH.

Set registers DRV:

Driver Control=00000040

OCP_ACT Asociated HB is shdn.

VCP and VGLS UVLO fault ena.

Gate DRV fault ena

1x PWM mode

1PWM_COM async rect =0

1PWM_DIR =0

BRAKE =0

Gate Drive HS=000003FF

Gate Drive LS=000007FF

OCP Control=0000016D

CSA Control=00000283

Reserved=00000000

After this settings when DRV was still OK: set INLC HIGH motor started rotating and speed depends on PWM duty and power supply.