Please let us know about PVDD_UVLO2 of DRV8305NQPHPRQ1.

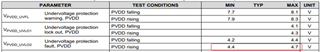

The threshold value of PVDD_UVLO2 is stated as 4.4 to 4.7V on the data sheet.

Is it possible to enter P VDD_UVLO2 even at voltages above 4.7V due to variations of IC?

(For example, when PVDD: 5.85V)

What is the actual variation range of the threshold value?

Regards,

Kura