Hi Team,

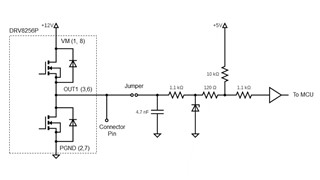

Developing a board in which a connector a pin shares the half bridge output of the DRV8256P with an open collector input, as shown in the following diagram:

The idea was to configure the board in two ways:

Configuration 1 - Use connector pin as Half bridge: Remove the jumper connecting the input circuit from the full bridge output. That works as intended.

Configuration 2 - Use pin as input: Set nSLEEP low, so that the full bridge output is in Hi-Z and connect a open collector type circuit to the connector pin.

The problem is that even in sleep mode, the full bridge output still draws current. I've made some measurements and it appears to draw current as if connected to a 1.8kOhm resistor to ground, even when we change the pull-up resistor.

If they connect a low enough pull up resistor to the 5V (about 500Ohm instead of the 10kOhm) I can make the input work as intended, but depending on the open collector we connect to the output pin, the current might be a little too high.

They can't understand why the low side MOSFET would draw current when the device is in sleep mode. Is there anything I can do to make sure that the half bridge output truly stays at high impedance?

Hoping for your assistance.

Thank you.

-Mark