Hello

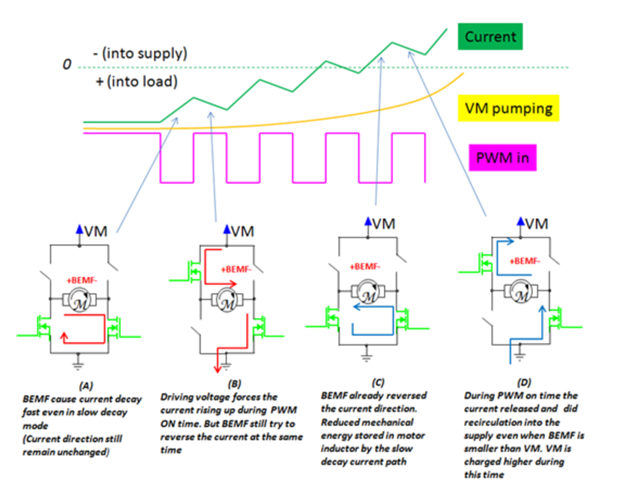

We are using the DRV8703-Q1, to drive a 30V/350W PMDC motor, with suitably sized MOSFETs (1.9mOhms / 60V). When we stop the motor (via Signals PH/EN), we are seeing physical failure (package burnout / damage) of the DRV8703-Q1. This happens at 100% PWM as well as lower PWMs. We are not decelerating the motor in this case, its an abrupt stop (emergency stop).

There is no load on the motor, just a gearbox.

We are seeing two types of failures

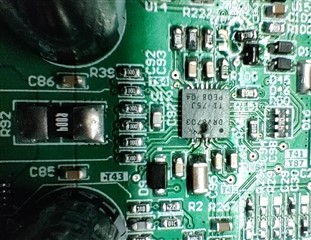

1. The physical failure is near the Vm pin (physical proximity - this may not be the Vm pin itself).

2. The physical failure is on the Vm pin(image below).

This is a HVM product and we need to get to the cause of these failures and fix them thoroughly asap to go into production. I can share more details as needed to troubleshoot these.