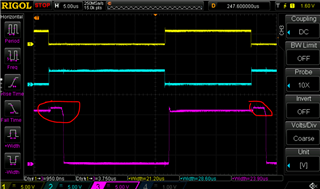

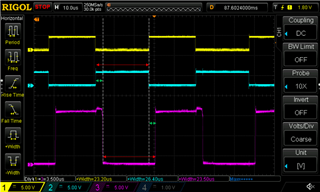

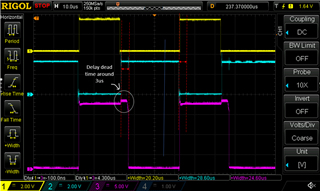

When running a calibration procedure, the DRV8316 output does not seem to match the input duty cycle.

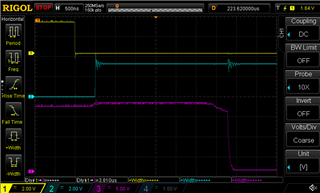

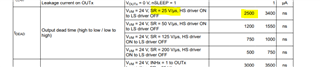

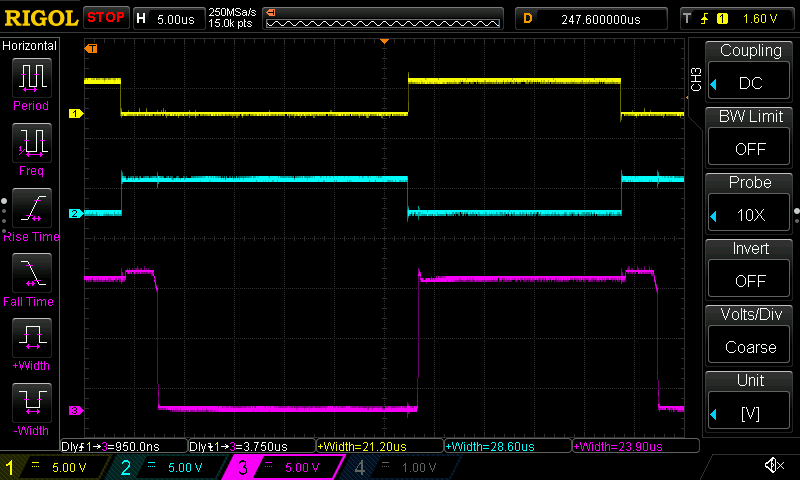

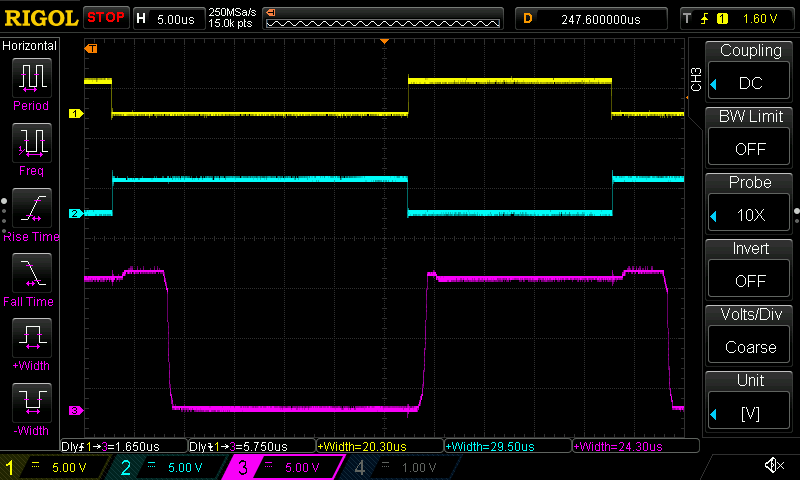

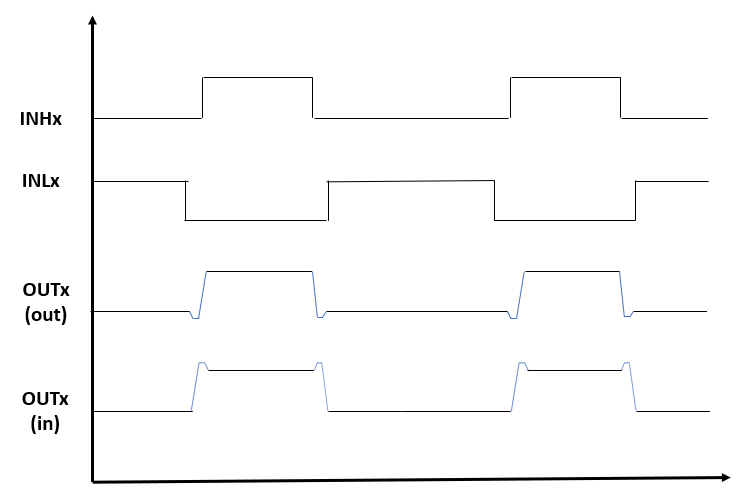

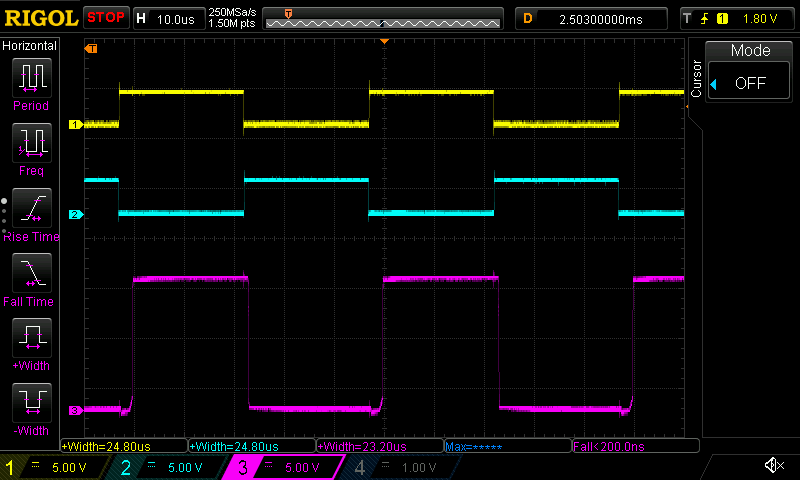

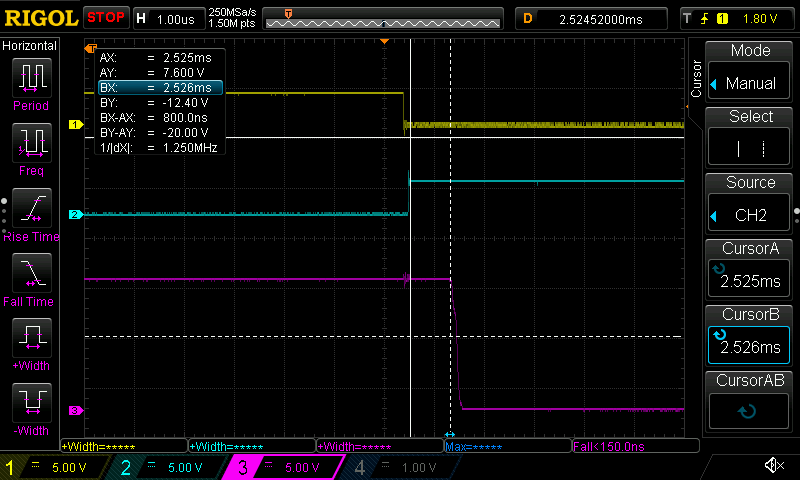

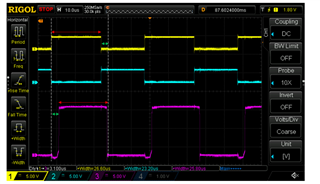

I am using 6x PWM (not current limit mode); I have configured the device over SPI, currently with the defaults other than OCP_DEG (0x2: 1.1us), and OCP_LVL (0x1: 24A). My PWM is 20kHz, and contains 500ns of dead time between HA/LA as per the nominal dead time listed on the datasheet. (Note that AAR and ASR are off by default)

For calibration of phase resistance, I force a set amount of current (3A) through a specific motor phase using a simple PI loop for 1 second, and record the estimated phase voltage based on the requested modulation. The current is correct, measured at 2.95A; however the PWM duty cycle the PI controller applies to reach that level implies a much higher modulation than is actually seen on the motor phases.

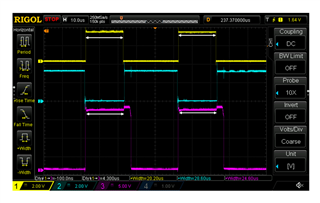

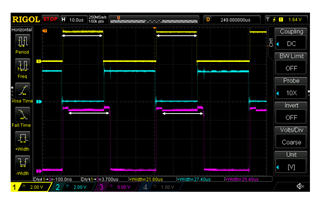

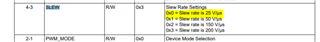

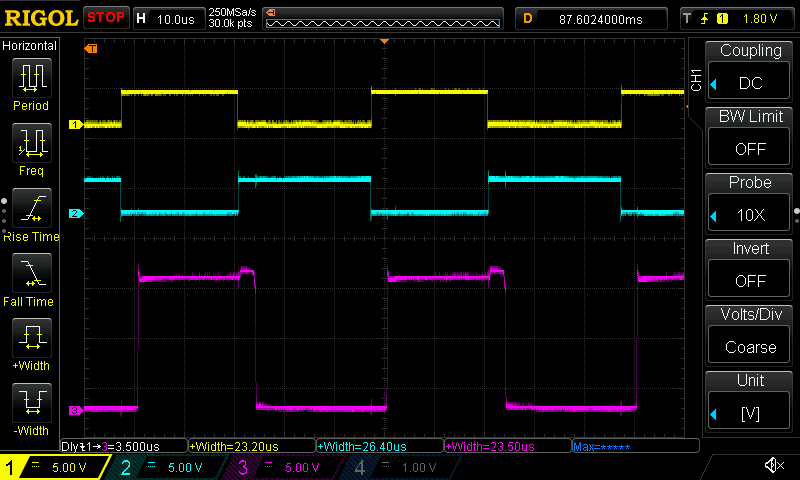

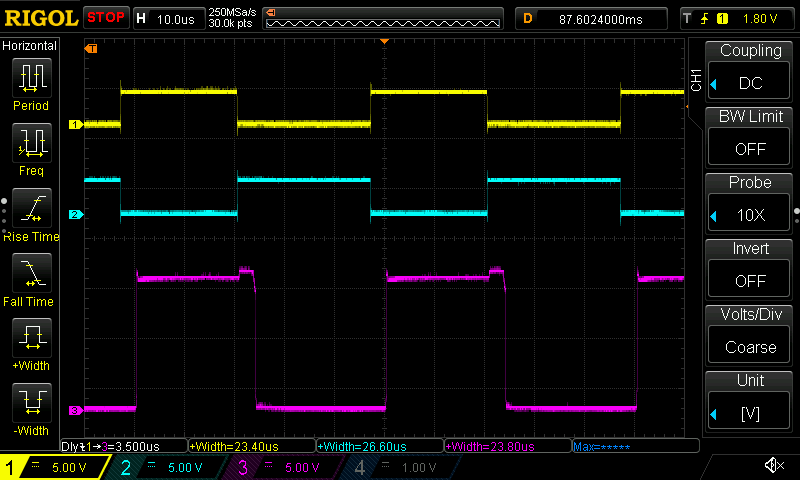

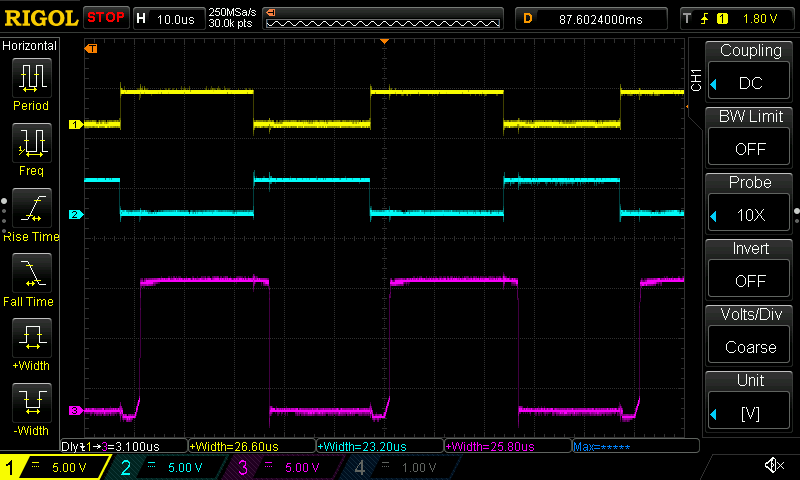

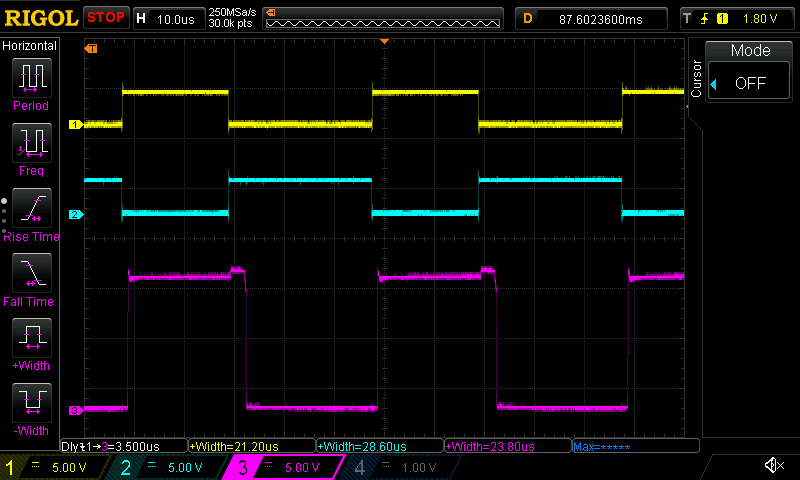

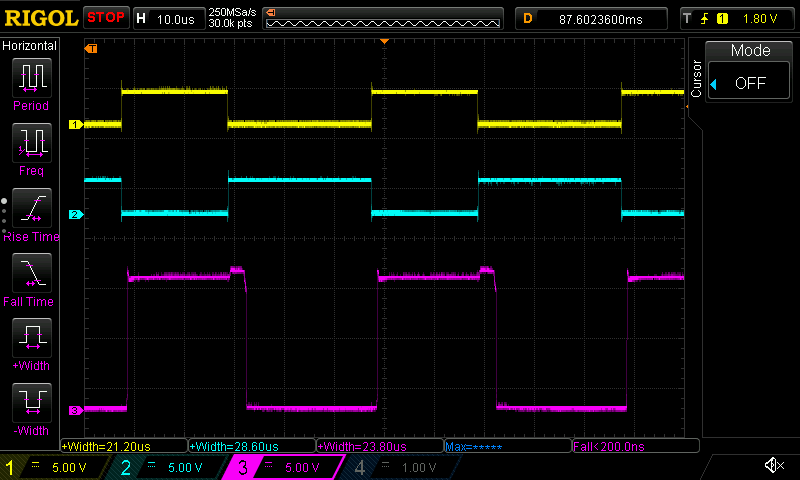

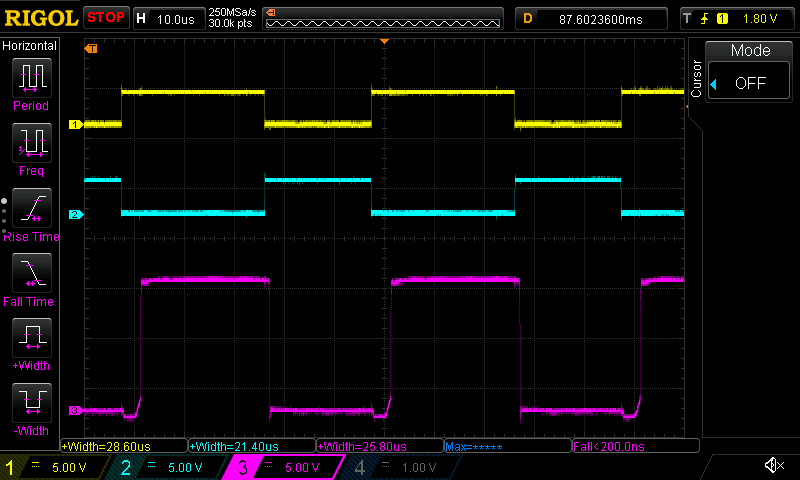

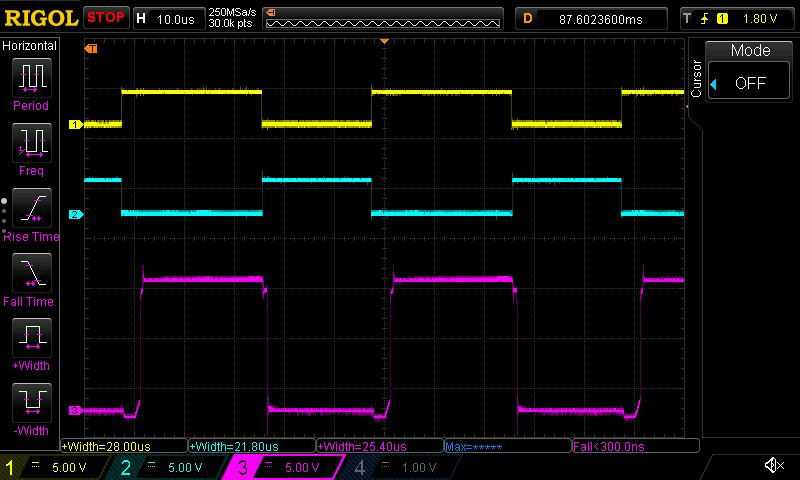

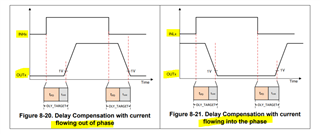

I have tried to use the Driver Delay Compensation to make the output duty cycle match the PWM inputs more closely, and it does work to make the duty cycle less distorted. However, even using the highest delay target (0xF) of 3.2us, the output is still significantly distorted to make the calibration significantly different than expected.

I have attached a zip of some oscilloscope traces showing the delay and duty cycle distortion. If anyone has any idea on how I might be able to make the applied duty cycle more accurately resemble the input PWM, I would appreciate it!

Thanks,

Eric