Hi experts,

When my customer using DRV8803 as PLC DO driver.There are some questions I would like your comments for deeply explain our datasheet features.

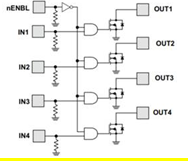

- Q1:In below nENBL and RESET features, what is the difference between nENBL and RESET? Can I think of RESET low is normally transport signal from in to out?

|

Pin |

I/O:High (1) |

I/O:Low(0) |

|

nENBL |

Disable output drivers |

Enable output drivers |

|

RESET |

Reset internal logic(Input ignored) |

Normally input? |

- Q2: What does RESET active high actually mean? Do we active RESET internal logic by switch off Nmosfet internally? Or any other ways?

- Q3:What is the port status of the input if RESET set active high? It has internal pulldown resistor does it mean reset the I/O status to 0?

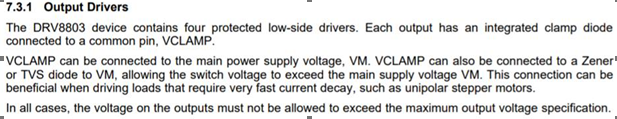

- Q4:In below features we mentioned Vclamp has two ways of connection. But can we float the Vclamp instead? What is the consequence if float Vclamp? Customer has another power supply to connect VM. They don’t want to connect VClamp to VM.

I am looking forward to your reply and have a good day! Thank you!