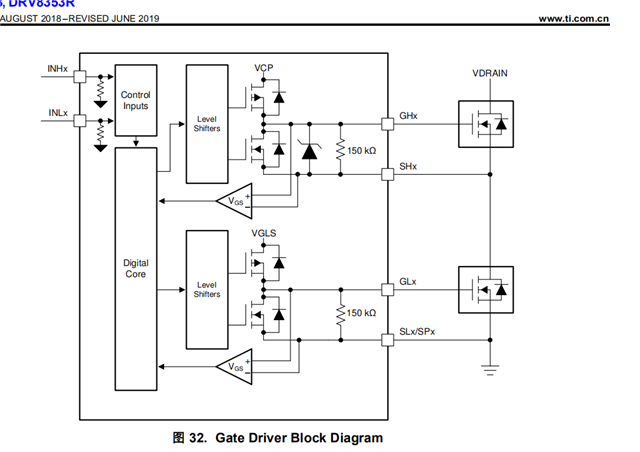

I see the datasheet that

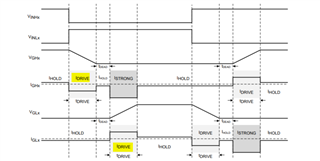

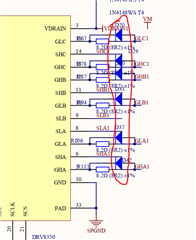

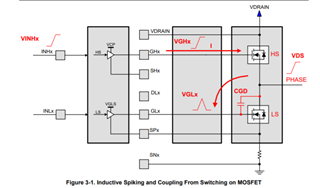

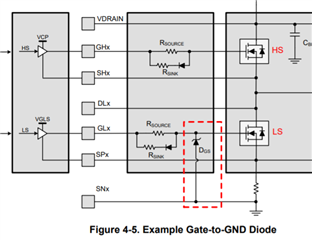

Then glx is short to pgnd and shx or vm.It means that the Idrive is too low and should be shorted to the pgnd、shx、vgl

But this days I have two pcb whose Idrive_LS and Idrive_HS are the smallst value (50mA or 100mA).But I found that the glc pins is

shorted to the vgls 。Does it also means that the idrive is too low? Besides the tdrive is the max value and the ghx ara all goond.

thanks

shengzhong