Other Parts Discussed in Thread: DRV8305,

Thank you for your support.

Our customer has a question about about VDS_OCP of DRV8305NE.

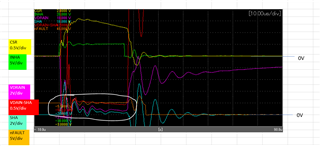

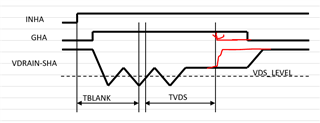

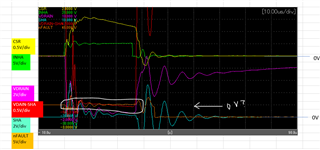

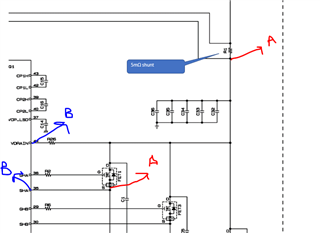

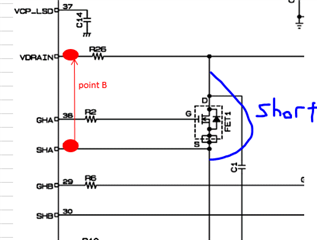

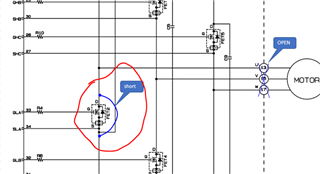

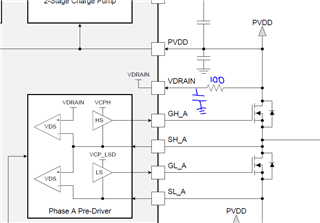

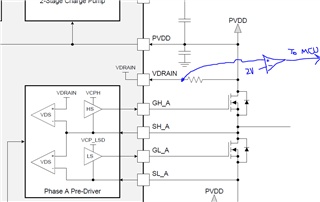

The customer shorted the drain-source of the FET in the lower stage of the U phase (A phase of IC ) and confirmed the operation of MOSFET Overcurrent Protection (VDS_OCP).

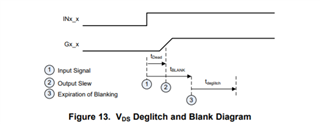

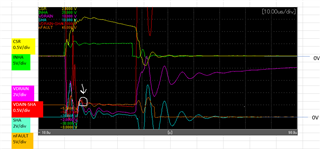

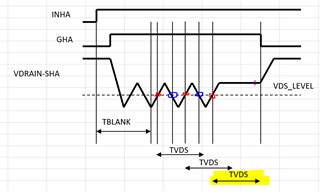

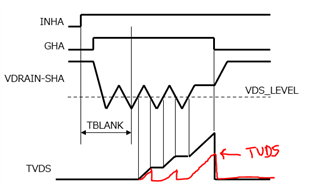

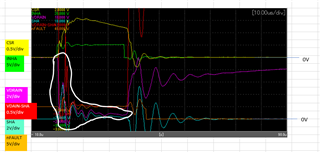

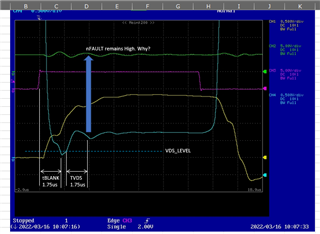

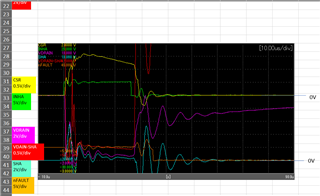

The IC did not detect a short circuit even though the voltage of VDRAIN-SHA exceeded the threshold value of 155 mV for 20us.(Refer to the "Waveform" sheet in the attached Excel)

What is the cause of this?

For register settings, refer to the "Control Register" sheet in the attached Excel.

Regards,

kura