Other Parts Discussed in Thread: DRV8871

Hi,

the DRV8874 datasheet specifies tDEG current regulation deglitch time as 0,6us, but I observe that the bridge trips 5us after Itrip at high dI/dT.

IPROPI follows the measured current perfectly, so this seems to be an internal delay.

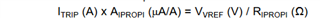

Setup: Vref=3.3V, R-IPROPI=2k4, IMODE = GND, VM=12V, static IN1=H, IN2=L, load inductance 1mH or 66uH.

The scope screenshot shows the output current (blue), V-IPROPI (pink) with 66uH load and output current with 1mH load (reference/white).

As you see, the DRV8874 trips at approx. 3A with slow dI/dT, but it trips at 3.77A at dI/dT=0.165A/us, or 5us after passing the 3A mark.

What's going on?