Hello,

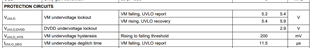

When VVM drops below its Min operating range 5.5 V in a system shutdown sequence, for example, and then it rises again on the way (3.3 V, for example) before reaching 0 V, will the DRV8343S-Q1 always successfully restart? Or, can it fail? How will the DRV8343S-Q1 behave?

In this case, 5.5 V is always applied to the ENABLE pin regardless of the VVM voltage.

Best regards,

Shinichi Yokota