Hi team,

Looking at the datasheet, I'm curious if there's a SPI transfer timeout for the communication. Another description would be is there a time where, if the SPI communication takes longer than x micro/nanoseconds the communication times out.

Does that exist?

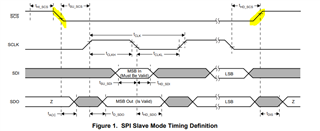

Working off the specs given in the datasheet, the SPI timing requirements has the minimum SPI clock period at 100ns (Table 6.6). During SPI communication, the DRV8305 is looking for 16 bits of data (Section 7.5.1.1). If the data to SDI =/= 16 bits, then it’s considered a frame error and the communication is ignored.

Multiplying it out, I’d think that anything longer than 1600ns would not be valid. I guess another way to put it would be that SPI commands would all have to execute within 1600ns to be valid.

Is that accurate?

Thanks,

Jacob