Other Parts Discussed in Thread: DRV8426

Hi,

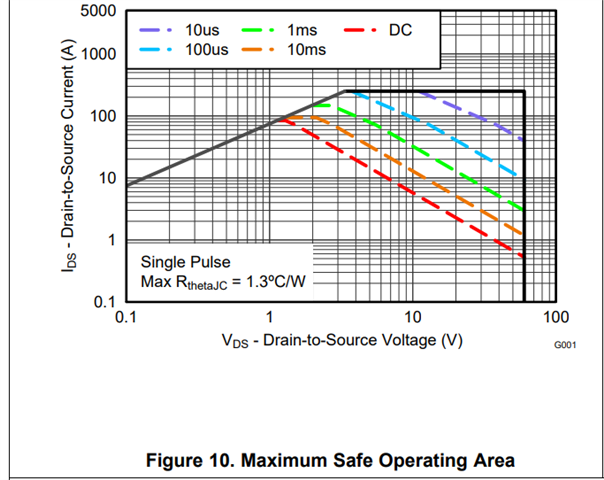

Is there any data about the SOA of the FET as shown in the graph below?

Best Regards,

Nishie

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

Hi Nishie,

Can you specify what you mean? Do you mean an SOA voltage vs current graph? Or are you looking for information about the LS FET of phase A in regards to its IV characteristics?

CSA outputs (SOx) support up to 30pF capacitive load, 0.25 to VREF-0.25 voltage range, and up to 1kohm series impedance.

Thanks,

Aaron

Hi Aaron,

Thank you for your reply.

At the time of OCP, I think that the current exceeding the threshold value flows for the diglich time times Iocp.

Specifically, current such as VM / Rds.

I want to know SOA from this point of view.

For SOA data, I want a graph like drain to source current vs drain to source voltage.

Best Regards,

Nishie

Hi Nishie-san,

SOA is the output of the current sense amplifier for phase A, which will be equal to Vref/2 +/- GAIN x IOUTA (see equation 3 in the datasheet, assuming you are operating the device in VREF mode instead of ILIM mode). IOUTA is the current flowing through the low side MOSFET of the half bridge. For OCP, you can set the OCP trip threshold to either 16A or 24A. If the current that the device measures through the low side MOSFET exceeds the OCP trip threshold current, and that threshold is exceeded for longer than the OCP deglitch time, then the device will Hi-Z the outputs. Keep in mind that the peak current for this device is 8A, so the OCP feature is more for protection in the case of hard shorts on one of the phases. The SOx CSAs, on the other hand, are primarily for monitoring the current during normal motor operation which can be fed back to an MCU to control the PWMs applied to the DRV.

You can estimate how much current is flowing through the phase by looking at the VDS voltage of the MOSFET while the MOSFET is on, and using the approximate rds(on) of the MOSFET to get an approximation of the drain to source current through the MOSFET. IDS = VDS/ Rds(on). So if the low side MOSFET is on, measuring the OUTx to GND voltage would be the approximate VDS voltage of the low side MOSFET, and the Rds on of the MOSFET for the DRV8316 is approximately 95mohms/2 at room temperature, and those parameters can be used to get a rough estimate of the IDS current. Keep in mind the Rds(on) value will vary across device temperature and there will be some rds(on) variation from device to device (see the Rds(on) specs in the datasheet for more information).

Regards,

Anthony Lodi

Hi Anthony,

Thank you for your reply.

We apologize that our explanation makes you confuse.

As the background of our question,

During deglitch time of OCP, the current which exceeds OCP's threshold flows the motor device.

Maximum current will be VM/Rds in case of short condition.

Motor driver has FETs. We assume that these FETs have SOA(safety operating area).

By the view of SOA, the customer would like to know whether the driver will damage or not.

If this question contains confidential contents, could you let us know whether the device operates within safety operating area in case of OCP or not?

Best Regards,

Nishie

Hi Nishie,

Thank you for the clarification! I am looking into this in more detail, I will try to get back to you next week.

Regards,

Anthony Lodi

Hi Nishie,

I'm not sure if we have the graph available that you are wanting, however I can say that we have performed testing with the OUTx shorted to ground to test the OCP protection. During this test there was no damage that was observed on the device. We also performed the same test with OUTx shorted to VM, with similar results. So if the customer is primarily concerned about hard shorts to ground or VM, during our testing there was no damage that was reported.

During these hard short events, although the current that flows is quite large, the current through the MOSFET rises very quickly which causes the OCP threshold to be reached quickly so the duration of the high current is fairly short.

Hope that helps!

Regards,

Anthony Lodi

Hi Anthony,

Thank you your reply.

OK, we got that you don't have SOA data for DRV8316.

In case of short occurring, until the device operates OCP protection to stop FET, the following maximum current flows into device as the calculation.

-Ishort=40V/Rds with 1.6us(OCP deglitch time)

So, in this case, the device doesn't damage, right?

However, you have the designed data which the device endures from short current during maximum OCP deglitch, right?

And, by the view of heat dissipation, we assume following;

-OCP deglitch time : 1.6us

-Rds : 0.1Ω(nearly value)

-Ishort : 40V/Rds

-Ishort^2*Rds*tocp=0.0256W・s

Above calculation, heat dissipation is no matter for device damage.

Best Regards,

Nishie

Hi Nishie-san,

I need a little more time to look into the specifics of the OCP test that was done, I will try to respond by the end of the week.

Regards,

Anthony Lodi

Hi Anthony-san,

Thank you for your support.

OK, we are looking forward your update.

Best Regards,

Nishie

Hi Nishie-san,

The OCP test that was performed with the phase shorted to GND the current peaked at the end of the deglitch time to a little over 50A before the DRV shut off the MOSFETs and pulled nFAULT low. Similarly, with the phase shorted to VM, the current peaked at the end of the deglitch time to a little less than 60A before the DRV shut off the MOSFETs and pulled nFAULT low. In both cases no damage was observed to the device, including thermal damage. As long as the thermal design of your board layout is good, I don't see overtemp being an issue if an external hard short to ground were to occur since the duration of such an event is fairly brief with the OCP feature shutting off the outputs 1.6us after the current reaches 24A (for the max OCP setting).

Regards,

Anthony Lodi

Hi Anthony-san.

"With the phase shorted to GND the current peaked at the end of the deglitch time to a little over 50A before the DRV shut off the MOSFETs and pulled nFAULT low. Similarly, with the phase shorted to VM, the current peaked at the end of the deglitch time to a little less than 60A before the DRV shut off the MOSFETs and pulled nFAULT low."

->We would like to confirm “little over 50A”.

Is there is current limit circuit on OCP block?

Because, if there is no current limit circuit, we think that the current will be more than 50A like as followings;

-Ishort : 40V/Rds =400A

-Rds : 0.1Ω(nearly value)

And then, if there is no current limit circuit, the worst heat dissipation will be followings;

-Ishort : 40V/Rds=400A

-OCP deglitch time : 1.6us

-Ishort^2*Rds*tocp=0.0256W・s

Is our recognition correct?

Best Regards,

Nishie

Hi Nishie,

In reality the current does not rise instantaneously, so the current is still rising when the OCP protection circuit shuts down the device. As a result, the observed current was less than 60A by the time that the DRV shut off the outputs. Also keep in mind with an external short to ground the drain of MOSFET is held at VM and the source is held at GND, which is different then normal operation when the MOSFET switches on so that the source voltage of the High side FET is pulled to VM when switching on. The 100m ohm (HS+LS) Rds (on) value is based on typical operation where the MOSFET can switch normally, so with a hard external short holding the drain at VM and the source at GND that may effect the RDSon value of the MOSFET during that mode of operation.

Regards,

Anthony

Hi Anthony,

Thank you for your reply.

As a result, the observed current was less than 60A by the time that the DRV shut off the outputs.

->OK, we got the result and your opinion.

What we would like to know is following two points;

-Is there current limit circuit on OCP block?(DRV8426 has current limit function on OCP block.)

-By the view of worst heat dissipation, we recognize that there is no problem so the device can endures 400A 1.6us. Is it correct?

Could you let us know these?

Best Regards,

Nishie

Hi Nishie-san,

I do not believe there is a current limit block on the DRV8316 that is implemented before the OCP fault triggers, but I will confirm.

I am not sure whether or not the device can endure 400A for 1.6us from a thermal perspective, since the test that we performed for OCP resulted in less than 60A of current, not 400A. But I can say that no thermal issues were observed when the OCP feature was tested with a short on the phase. The device also has a thermal overtemperature shutdown feature that will shut down the outputs if the temperature of the DRV exceeds the overtemperature threshold to protect the device. Thermal performance is going to depend heavily on the PCB layout, so ensure a wide cooper pour connected to the thermal pad to give good heat dissipation. Copper on the top and bottom layers dissipate heat better since they are exposed to the outside air.

Regards,

Anthony Lodi.

Hi Anthony-san,

I do not believe there is a current limit block on the DRV8316 that is implemented before the OCP fault triggers, but I will confirm.

->OK, we are looking forward to your update.

I am not sure whether or not the device can endure 400A for 1.6us from a thermal perspective, since the test that we performed for OCP resulted in less than 60A of current, not 400A.

But I can say that no thermal issues was observed when we repeatedly tested the OCP feature with a hard external short.

->OK, we got your result and your opinion.

Is following heat dissipation OK.(it might depend on PCB layout.)

-Rdson(H+L)=0.1ohm

-40V/Rdson(H+L)= 400A

-400^2x0.1 = 16000W

-16000Wx1.6us=0.0256Ws

Best Regards,

Nishie

Hi Nishie-san,

I will try to get back to you tomorrow.

Regards,

Anthony Lodi

Hi Nishie-san,

I confirmed that there is no current limit block that is implemented on the device prior to when the OCP fault triggers. Inductance in the current paths in the device could slow down the rise of current, which could be a contributing factor as to why the current doesn't rise as quickly.

Heat dissipation will depend on PCB layout, I am not sure if that heat dissipation described in your calculations will be OK. If the temperature of the DRV rises to the thermal shutdown temperature, it will immediately trigger an OTSD fault and shut down the DRV to help protect it from damage, so even if the thermal dissipation was an issue there is a protection feature to help keep the temperature from getting too high.

Some of the values you used in the formula to calculate the power isn't very applicable in the condition where there is an OCP fault that occurs due to a hard short to ground, because the current doesn't rise all the way to 400A by the end of the deglitch time, but it instead was observed to rise only to less than 60A. Using 400A in the power calculation doesn't reflect what is actually observed when an OCP fault occurs.

From a thermal perspective, as long as you follow good layout practices to help with thermal dissipation, I don't see any concern with thermal damage either in the case of the OCP tripping due to a hard short to ground.

Regards,

Anthony

Hi Anthony-san,

Thanks for your comment.

Could you provide me with the data of test results?

Best Regards,

Nishie

Hi Nishie-san,

I have followed up with you over email regarding this.

Regards,

Anthony Lodi