Other Parts Discussed in Thread: DRV2700

Hi team

Here're some issues from the customer may need your help:

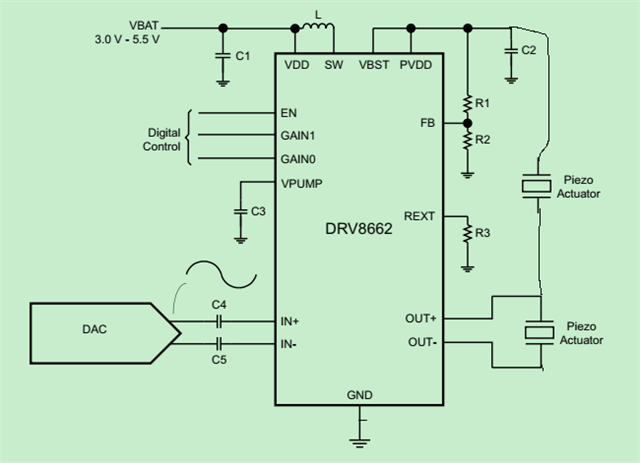

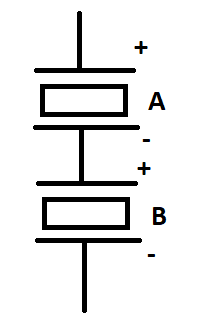

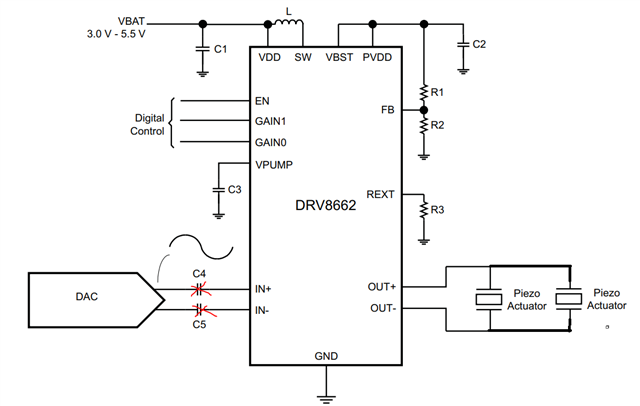

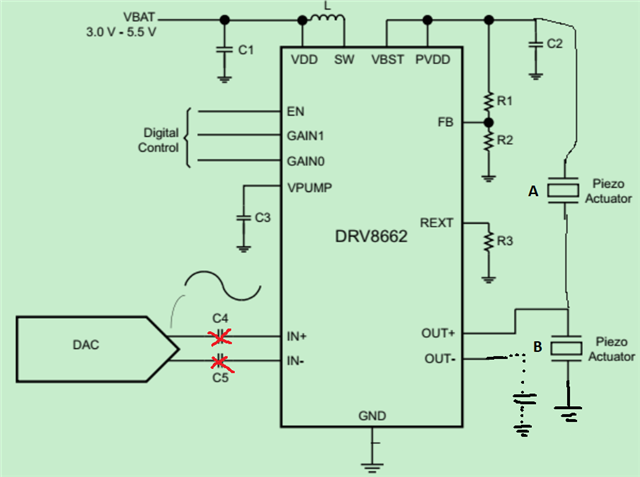

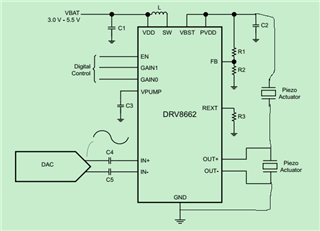

1) In actual applications, a piezo deflection mirror with two cascaded piezo ceramic whose length difference determines the angle of the platform they support after applying different voltages. Each piezo ceramic is polarity-driven and the negative voltage cannot be higher than the positive voltage. Can this chip guarantee that OUT+ is always greater than OUT-?

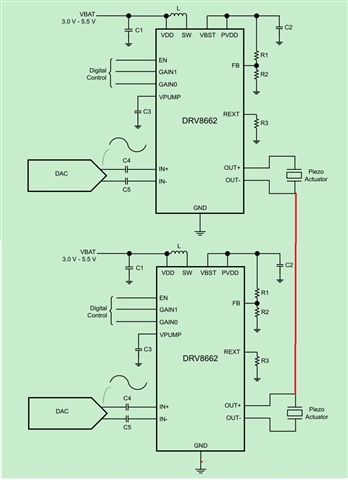

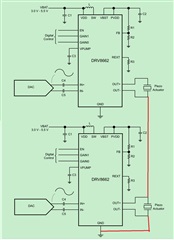

2) Can the two piezo ceramic that have been cascaded be driven as following figure? The next set of OUT- terminals is connected to ground and its OUT+ is connected to the OUT- side of the previous set. The effect is that for the following group, OUT- is fixed to GND, and for the above group, OUT- is followed by OUT+. The manual does not seem to mention whether or not the voltage of OUT- can be specified. Dose it have to be floating as shown?

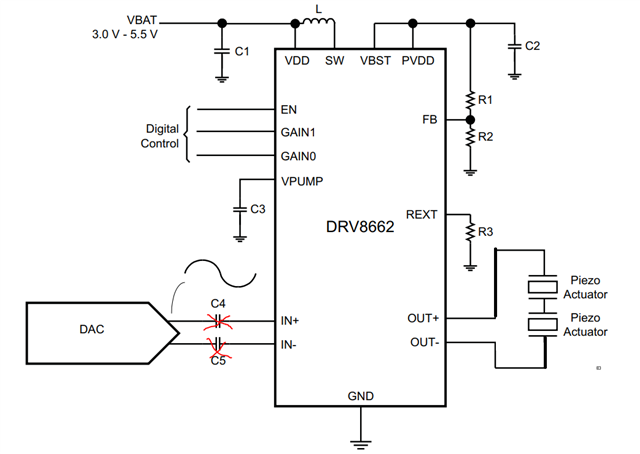

3) And regarding the following 4 threads, which are confusing, can input be a DC signal that keeps the OUT voltage in a constant state?

DRV8662: Coupling capacitor - Motor drivers forum - Motor drivers - TI E2E support forums

DRV8662: Single-ended DC operation - Motor drivers forum - Motor drivers - TI E2E support forums

DRV8662: input signal form for DRV8662 - Motor drivers forum - Motor drivers - TI E2E support forums

4) Is it possible to drive two cascaded piezo ceramic as shown below? The total voltage of the two piezo ceramics is constant at, for example, 100 V.

5)a. What is the duty cycle of the output voltage versus the PWM signal if a PWM input is used?

b. How does the drive chip identify whether it is a PWM signal or an analogue signal? Or is it that the drive chip does not recognize, and the external filter of the chip will smooth the PWM signal into an analogue signal?

c. If IN+ is greater than IN-, is OUT+ greater than OUT-?

Could you help check this case? Thanks.

Best Regards,

Cherry