Hello team

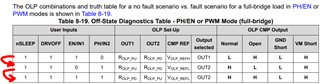

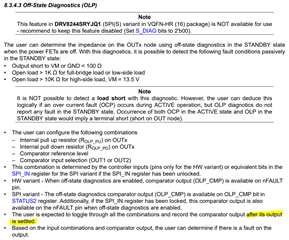

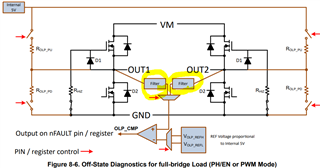

When we do the OLP, how long should we wait to get the true OLP CMP Output?

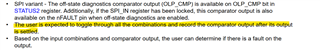

There is a description of the "record the comparator output after its output is settled."

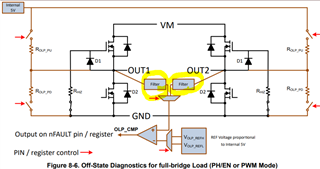

And there seems a filter circuit at the input of the comparator.

So I assume we should wait for a certain time to get true value of the OLP CMP output.

Thanks in advance.

Regards,

Hirata