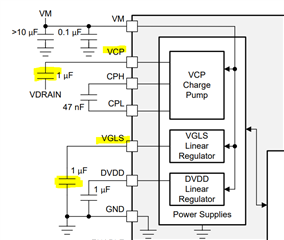

The datasheet for the DRV835x 100-V Three-Phase Smart Gate Driver mentions (on Page 68) that "IVCP/VGLS is the charge pump or low-side regulator capacity, dependent on the VM pin voltage." However, I cannot find additional information regarding the dependence of IVCP/VGLS on VM. Please provide the dependence.

-

Ask a related question

What is a related question?A related question is a question created from another question. When the related question is created, it will be automatically linked to the original question.