Hi Team,

We received this inquiry from our customer.

We are having problems with DRV8353 IC can you help?

Problem is IC fails when we increase sink source currents

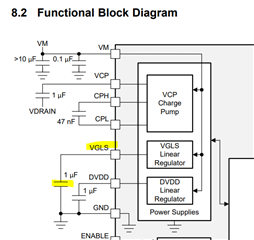

VGLS voltage fails and does not drive low side mosfets

We were using 150ma-200ma for high and low side. For a year there was no problem.

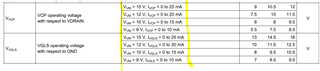

After we increased it to 300ma-600ma motor run for few minutes and we got VGLS UV error

We measured VGLS and it was 4.1V

Then it recovered to11V, cleared error

But not when we try to drive motor we get MOSFET drive error from Low Side MOSFETS

When we scope it we can easily see high side works but no change at low side. I cannot drive low side.

Motor specifications: 48V 350W BLDC, 20 pole pair.

Phase current was around 12A I assume during that few minutes.

Regards,

Danilo