Hi,

I have a bldc design witch is using the DRV8320H.

Everything works as expected but on some rare occasions, the Driver together with a shot thought happens.

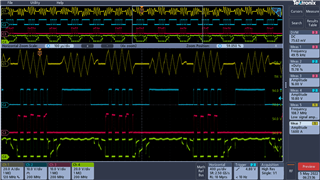

The instances when this happens are at a high current 30-40A close to 100% duty PWM and rapid variations from 70-100% duty.

The device is with Idrive tied vdd so that means 1A with 2A. Wonder if this might be a motive to worry about... the fets would work with lower.

I had 2 such failures where the driver exploded current seemed to flow somehow between a Low side Gate (trace broken by current) and VCP (the VCP 1uf cap was carbonized).

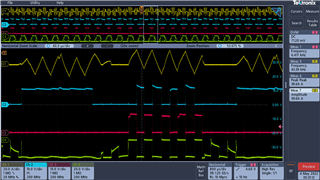

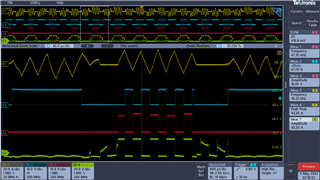

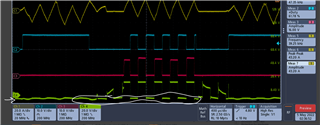

I did not work myself with a smart driver until now so I am not that familiar with it. But after having these problems I started investigating waveforms and I noticed that the Low and High sides look funky.

My SLx pins are connected to common Ground and IDRAIN to VM and OVCP is off. (implemented on the MCU based on current read on low side Sources)

Any hints would ve very much appreciated.

Gabriel