Hello!

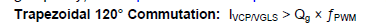

We're facing some problems with the DRV8353SRTAT.

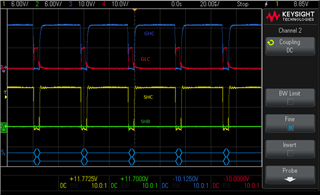

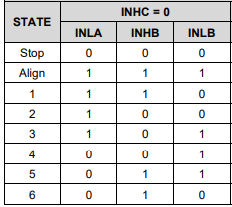

When in "synchronous 1x PWM" mode, as shown in the register table below, a fault ocurrs when changing from any state to another (see the table below):

| REG_0x00 | 0x0 | |

| REG_0x01 | 0x0 | |

| REG_0x02 | 0x40 | |

| REG_0x03 | 0x3ff | |

| REG_0x04 | 0x7ff | |

| REG_0x05 | 0x16d | |

| REG_0x06 | 0x283 | |

| REG_0x07 | 0x0 |

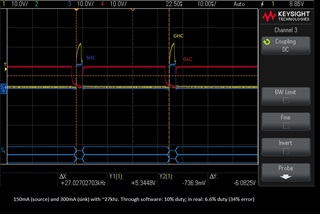

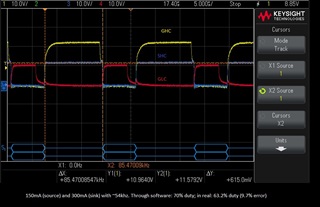

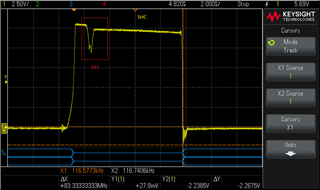

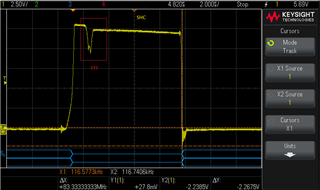

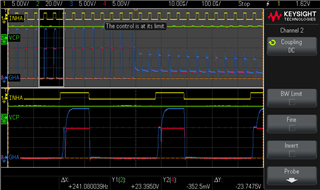

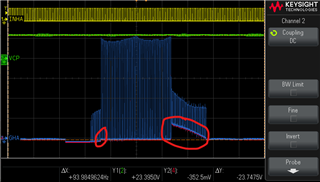

For example, going from "stop" -> 4, with no load attached (only testing signals on the oscilloscope), this change ocurrs well, but sometimes a "gate drive fault on the B low-side MOSFET" occurs. When the change is 4 -> "stop" it aways leads to the same fault (gate drive fault on the B low-side MOSFET) , as registers shown below:

| REG_0x00 | 0x500 | |

| REG_0x01 | 0x4 |

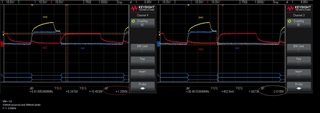

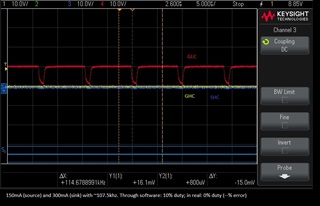

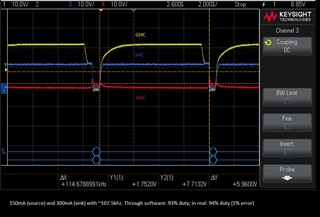

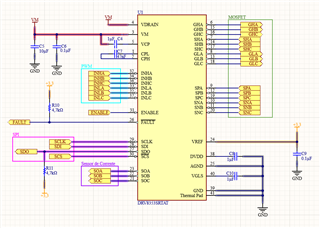

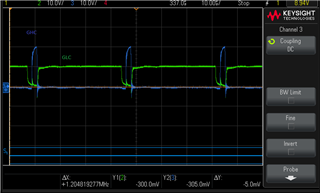

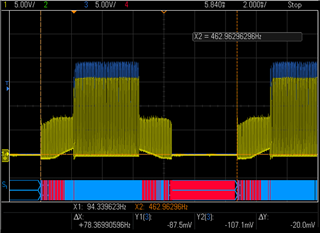

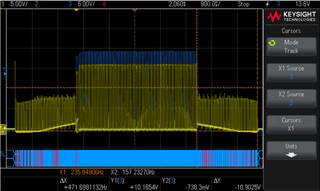

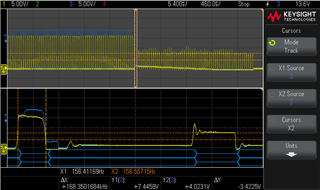

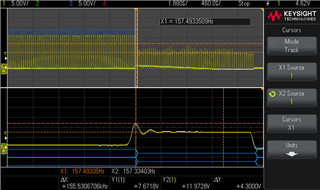

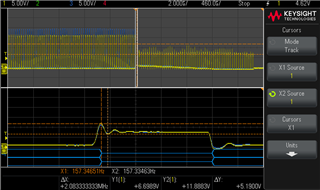

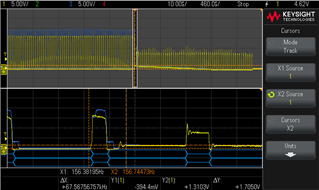

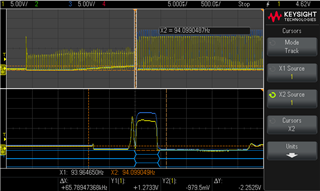

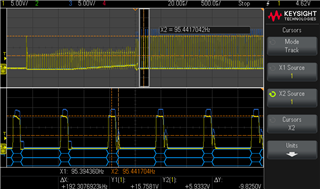

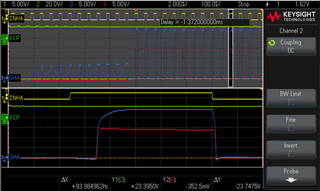

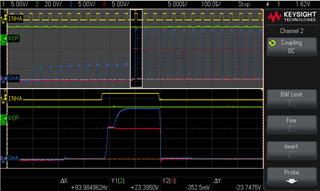

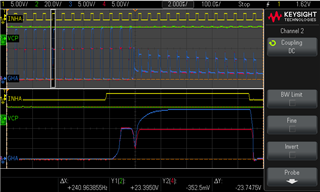

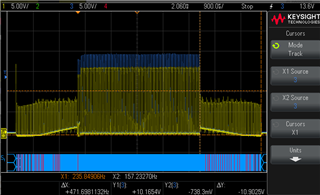

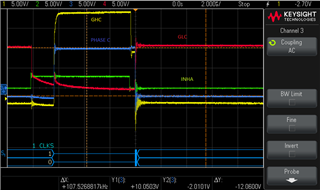

Below, a oscilloscope print of the MOSFET's GHC and GLC signals, as well as Phase C and INHA's PWM signals, where all reference gnd are at the same place as "blue gnd":

Some importante data:

Voltage: 12v

F ~= 195kHz

Mosfet: IRFS7530 (Qg = 236nC typ.)

If possible, I would like to be enlightened about the following questions:

1- Is this a high Mosfet Qg so that the fault occurs due to this? How to solve this problem? Is it needed to change the mosfets?

2- When transitioning between states on "synchronous 1x PWM", it's expected to be generated a fault? If yes, should we disable "Gate drive Fault" (address = 0x02h)?

3- What is the maximum recommended Qg and Qgs for the stable functioning?

4- Phase C and GHC lower level are both below GND. Is it normal? What does it means?

5- The GLC trace when goes low decays slowly, is this abnormal? What is this ripple at the "low" period?

Best regards and thanks for your help!