Other Parts Discussed in Thread: TMS320F28069M, , , , STRIKE, CSD88599Q5DC

Hello,

This is related to the thread

entitled "TMS320F28069M: Custom Board Design failing Lab 01c." I was working with Aaron Barrera at the time, so he's the most familiar with it.

Anyway, I made the changes requested, and ran the final design past Aaron. Then I got caught up in the communications aspect of this project for a couple months.

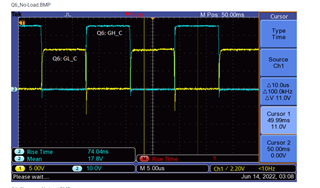

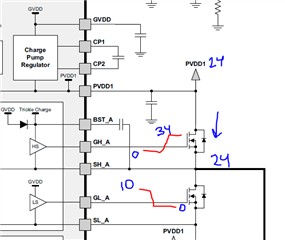

I just recently tried running the InstaSpin Labs again, and as soon as I set Flag Enable System and Flag Run Identify to 1, Q6 on my board starts spitting out smoke (it's only Q6 that's getting damaged).

The functional relationship between all parts is the same as the previous version, where I could at least get the motor to respond somewhat, without burning anything up.

The only changes were to the pcb layout - I'm now using polygon pours to widen the high current traces.

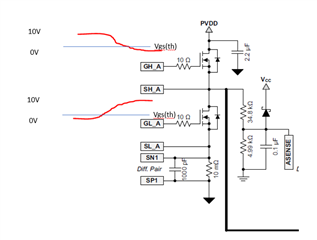

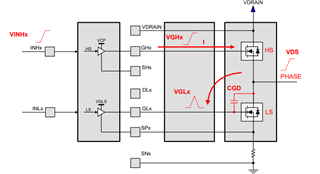

It almost seems like the gates of the 2 FETs in Q6 must be tied together, allowing 3v to be connected (nearly) to ground, but I already checked for that and ruled it out.

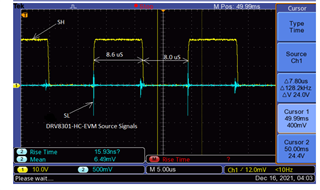

The other possibility that springs to mind is that somehow the firmware is turning on both FETs simultaneously, but this firmware works on the Evaluation Board (DRV8301-69M-KIT).

Thanks,

Dave