Hi Experts,

Good day. Seeking your assistance on this query:

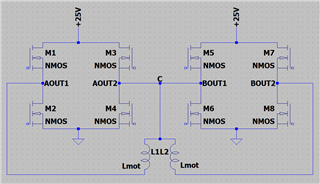

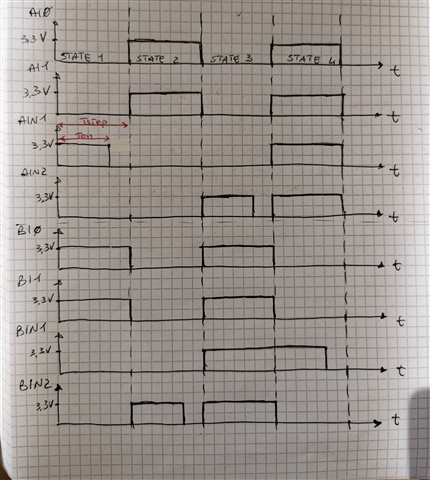

I would like to use the DRV8841 to drive a stepper motor. The issue is that this motor has a particular wiring and two phases, like shown in one of the attached pictures.

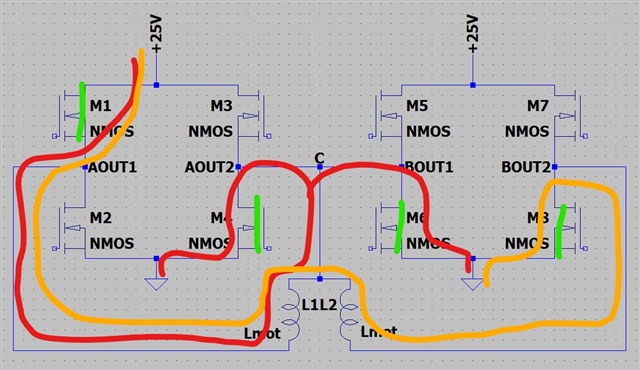

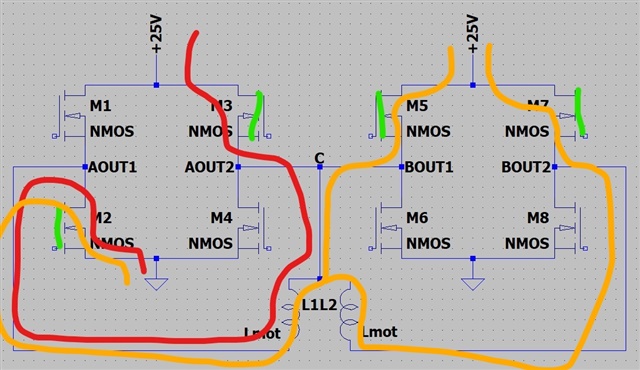

I would like to ask you if I can plug the common wire of the motor (C) to the H_bridges like it is shown in the example schematic I attached.

If the motor is excited like the excitation method that is shown, is there any risk that some short circuit can occur, or that the other phase may be energized when it shouldn't be?

Besides, when I set, for example, both the pins AI0 and AI1 to 0 (which corresponds to no current flow through the A H-bridge), the datasheet states that in this case that H-bridge is disabled. Does this mean that the outputs are in a high impedance state? So, if yes, no current can flow from the common point (C) to AOUT2 and then to ground through the low-side MOSFET (M4 in the picture)?

Thank you.

Regards,

Archie A.