Hi team,

Here's an issue from the customer may need your help:

The device has its own peak current protection, which is latched above the peak current, and must be reset before it can be released.

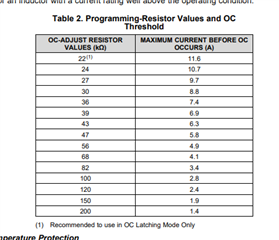

1) The customer would like to know if the peak overcurrent protection (OC) can be removed, since the manual simply states that the resistor can be adjusted to change the amount of peak current.

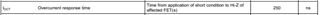

2) how long does the current last to trigger peak current protection, 10ms?

3) when reset, the reset pin needs to be pulled low and then pulled high. At least how long does the low level last?

Could you help check this case? Thanks.

Best Regards,

Cherry