Hello,

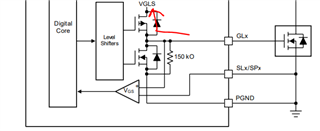

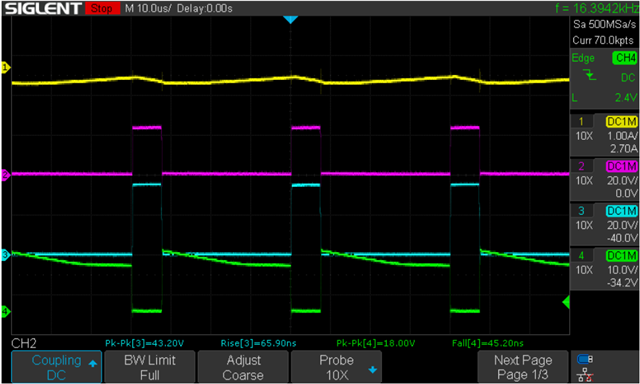

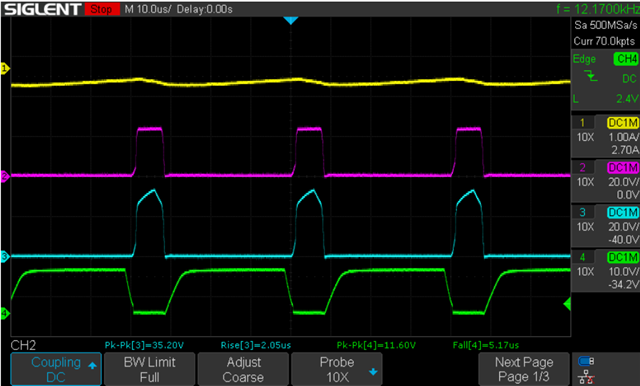

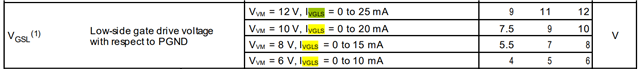

We were just wondering how the Vgls regulator works because it has the potential to damage our FETs. The datasheet does spec Vgls for VM > 12V... Our VM can go up to 35V and we want to ensure the Vgls doesn't go over 20V...

I saw another thread where a similar question was asked 5 years ago but no one answered.

Regards,

Jerome