TI Team,

Question on behalf of customer.

I just noticed some unexpected behavior with DRV870x chips samples, and I kindly ask for your support to identify the root cause.

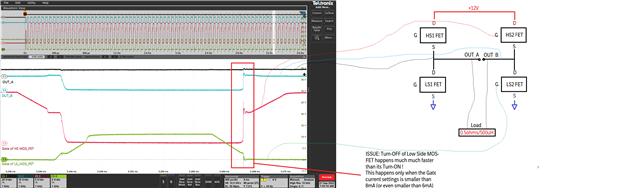

The trouble is that if the gate current setting is set to <6mA, the Turn-OFF of Low-Side MOS-FET happens very fast so practically there’s no slew-rate control in this case.

Please see below for more details.

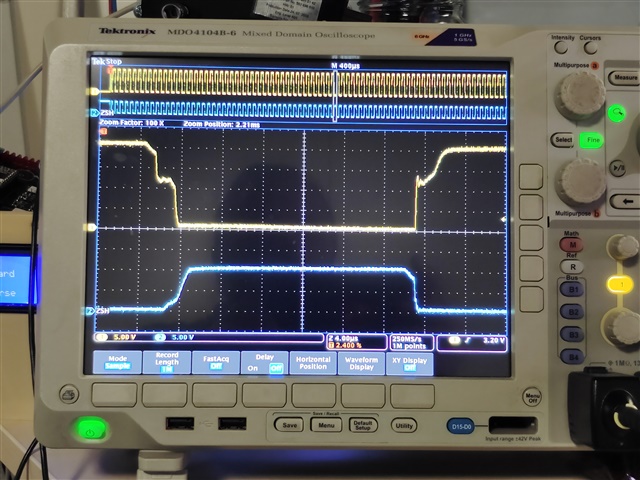

Behaviour when Igate is higher than 8mA

Behaviour when Igate is smaller than 8mA

I noticed that this issue:

- It occurs on the official TI Evaluation Board.

- occurs on LS2 MOS-FET for a gate current setting of 6mA or lower. For this I set the set the following control registers: DRV_CTRL_1 = 01010101 (for HS FETs) and DRV_CTRL_2 = 01010101 (for HS FETs).

- occurs on LS1 MOS-FET too, but for a gate current setting of 3mA or lower.

- occurs on both DRV8705 and DRV8706 (with the same thresholds of 6mA for LS2 and 3mA for LS1);

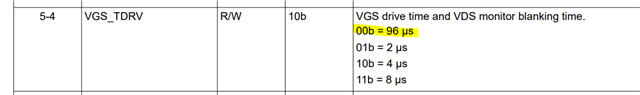

- occurs regardless of the Dead Time setting (I tested even the longest setting of 8us);

- occurs regardless of the load impedance (I tested loads between 0.5 – 10 ohms).

Given this:

- Assuming that the behavior is due to some Control Registry settings, can you suggest which of these settings I should check better?

- Can you suggest other tests/checks I could make to find the root cause of this behavior?