Hello,

I'm concerned about whether noise to the VM pin will cause IC reset.

The Data sheet said,

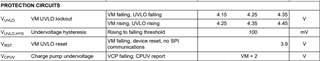

"When the voltage on the VM pin falls below the VM UVLO reset voltage (VRST, 3.9 V maximum), SPI

communication is unavailable, the digital core is shutdown, the FAULT and UVLO bits are low and the nFAULT pin is high."

How long does it take to reset if the VM voltage is kept below VRST ?

I couldn't find the description of the data sheet.

Please tell me. Regards,