Hi,

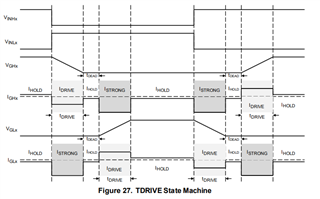

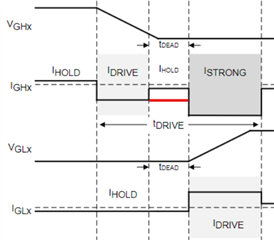

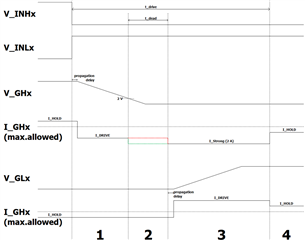

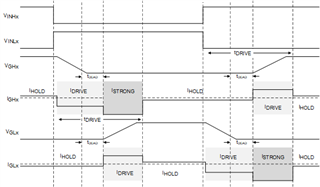

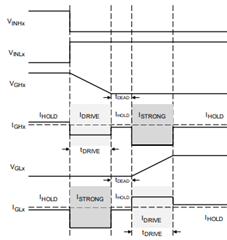

I've some question regarding the TDRIVE state machine. In the datasheets the gate current behavior is described as followed.

- The driven current (highside) is applied until the gate-source voltage falls under the threshold (2V)

- After reaching this threshold, the deadtime is injected and the hold current is applied to both (highside and lowside) FETs

- When the deadtime is over, the lowside FET is driven by Idrive

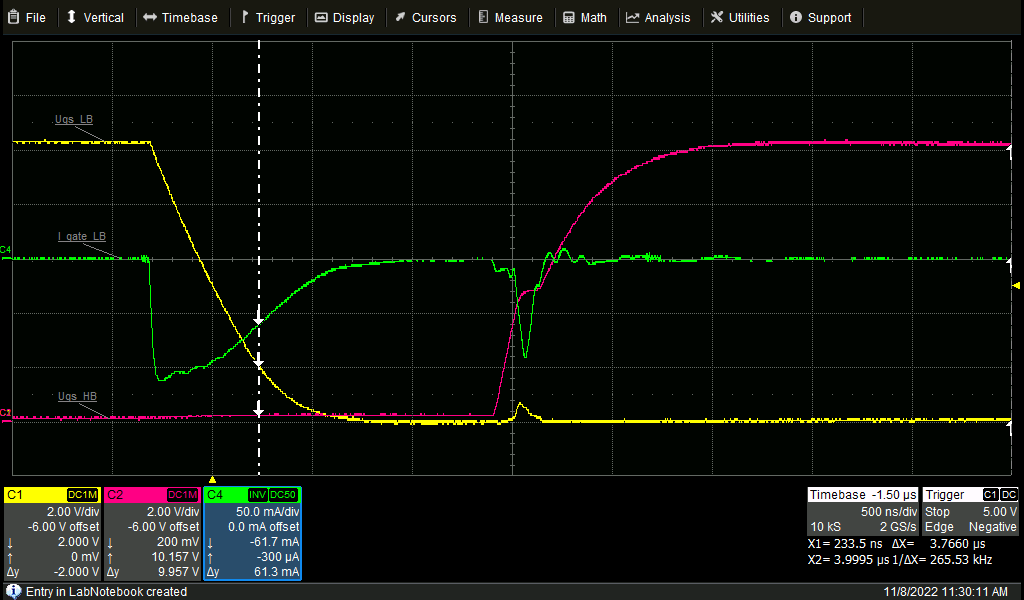

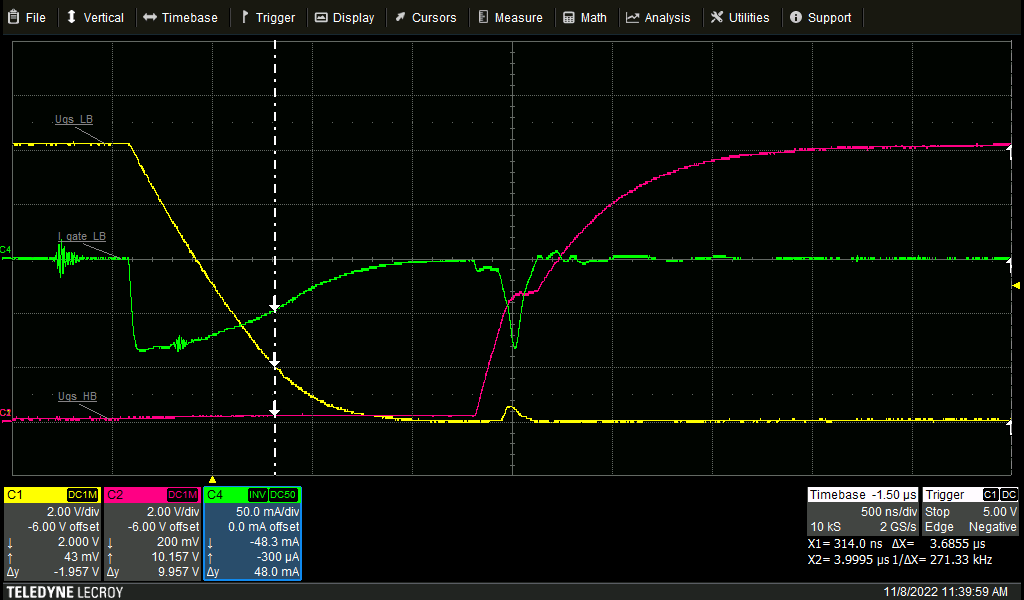

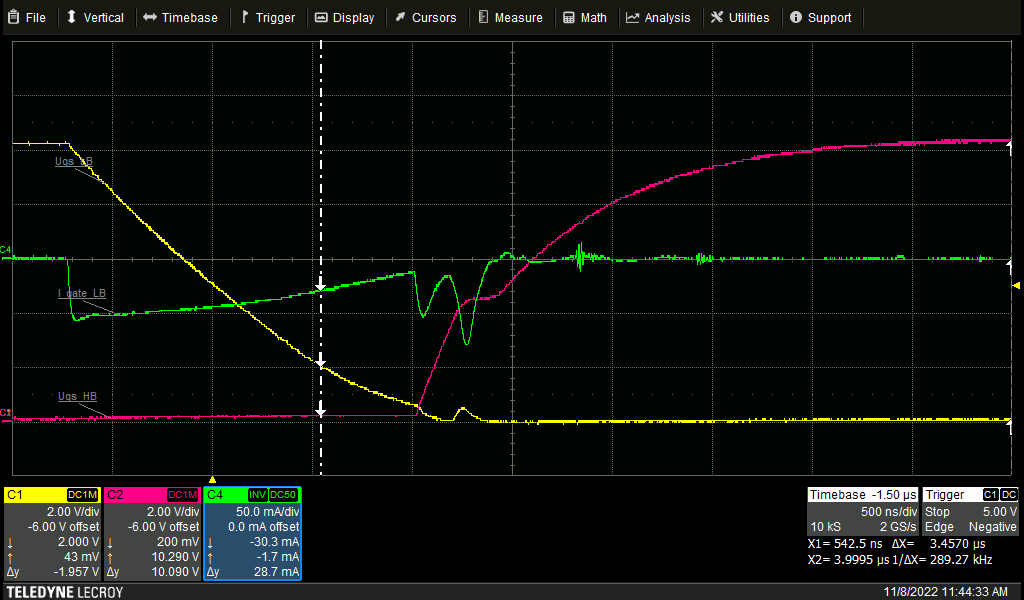

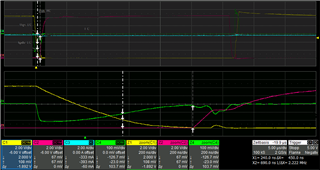

In my measurements I can observe a different behavior.

It seems like the driven current is also applied during the deadtime (between the cursors where U_gate-source_lowside is below the threshold of 2V). Should the driver reduce the current here to the IHOLD or is it intentional that the IDRIVEN is applied until the ISTRONG starts at the second cursor?

Can I expect a hard cut (e.g. within 20ns) from IDRIVEN to IHOLD when changing the TDRIVE states or is that a slow transition to the desired hold current?

C1: U_gate-source_lowside (yellow)

C2: U_gate-source_highside (red)

C3: phase current (blue)

C4: I_gate_lowside (green)

When switching on a FET, is there a threshold where the DRV detects a fully charged U_gate-source?

How does the TDRIVE state machine determines when the charge process is finished?

Thank you in advance for your help.

Kind regards

Tobias