Dear team,

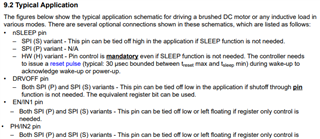

My customer hopes to use Register only control method to drive BDC. According to below description, I think it is feasible, and the register only control method can achieve the exactly same function with pin only control method, right? If they use this method, they can float IN1, IN2 and DRVOFF pins, right? Is there any risks here?

In addition, how to connect nFault pin if not used?

Thanks & Best Regards,

Sherry