Hi experts,

Could you please answer questions below about FAULT signal?

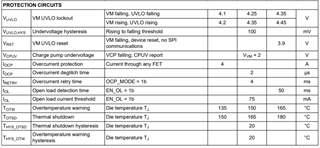

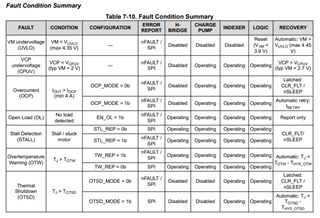

(1) Since the FAULT signal can be cleared by CLR_FLT (SPI) or nSLEEP (I/O), there is no condition that only CLR_FLT (SPI) or only nSLEEP (I/O) can clear it. Is my understanding correct?

(2) According to the datasheet, FAULT can be cleared in two ways, CLR_FLT (SPI) or nSLEEP (I/O). Could you tell me why you set up two ways?

(3) Since it can be cleared by CLR_FLT (SPI) or nSLEEP (I/O), is there any problem in using either CLR_FLT (SPI) or nSLEEP (I/O)?

(4) Is there a level (priority) set within the device for the FAULT condition?

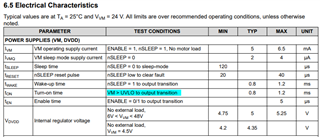

(5-1) When power is applied to the board, is it correct that the FAULT signal is Hi during the period when the VM of the device is at a low voltage?

(5-2) ( When power is applied to the board) If the UVLO bit is not cleared, it remains latched to Hi. So clear processing is required when the board receives power. Is my understanding correct?

Thank you for your help.

Best Regards,

Taito Takemura