Hi team,

Regarding the original post, the customer still have some motor driver issues may need your help:

The source code for the drive configuration for the 8323 in the SDK is the same as the customer's configuration and the data is not misaligned.

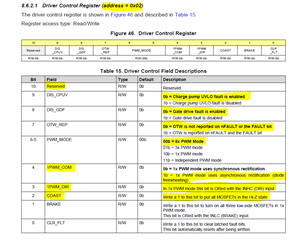

1) How to confirm that the data was actually written? According to the logic analyzer, 02 and 03 registers are written with return values. Whether write or read, 03 registers return values, but are not the same as written.

A write of the 02 register returns the value written by the customer but does not read any data.

Reads and writes of the 04-06 registers do not return a value, so the customer suspects that they did not write at all. However, from the output, the output value of the chip is changed after writing, enable pin is pulled high and CS has also done a corresponding action.

Does the register lock in register 03 have an effect on read and write? Or are there any pins in hardware that control SPI?

2) Assuming written is good and the customer wants to configure 1X mode (and automatically sensed by Hall), how to configure register values?

Now the value written to register 02 is 1052. However, from the actual hardware tests, the output is not the same as the truth table given in the data manual and the com bit does not seem to be written.

Could you help check this case? Thanks.

Best Regards,

Cherry