Hi Expert,

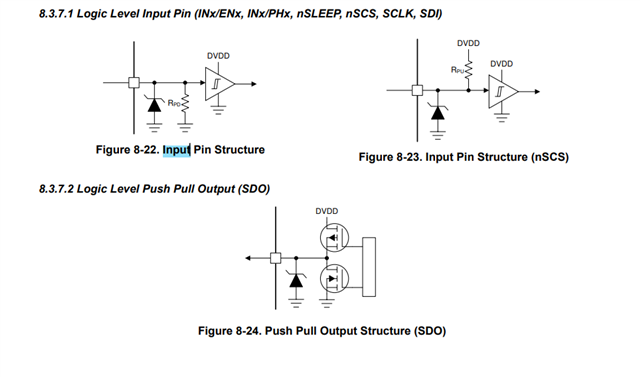

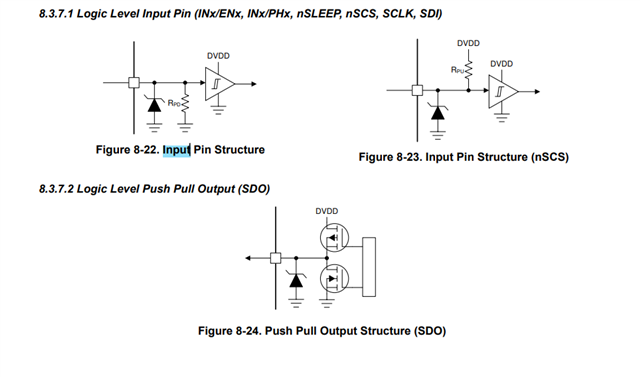

As found in DRV8718-Q1 d/s, for I/O structure of all the digital input and output pins, there is only pull down to GND ESD here. Why don't we need pull up ESD protection? Thanks.

BR,

Elec Cheng

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

Hi Expert,

As found in DRV8718-Q1 d/s, for I/O structure of all the digital input and output pins, there is only pull down to GND ESD here. Why don't we need pull up ESD protection? Thanks.

BR,

Elec Cheng

Hi Cheng,

The reason for only a pull-down on the input logic pins is to set the pin LOW in the case the pin is high-Z. Some of the input pins (nSLEEP, INx), It is preferable that the pin voltage is LOW in the case of high-Z so that it prevents accidental output enabled.

Regards,

Pablo Armet

As found in DRV8718-Q1 d/s, for I/O structure of all the digital input and output pins, there is only pull down to GND ESD here. Why don't we need pull up ESD protection?

I don't think the zener diode is for ESD protection. It probably is to claim the level safely at a predetermined value.

For ESD, it should be the symbol of 2 diodes back to back, not a Zener.

I assume you're not asking about the pull up or pull down resistor.

Brian