Hi Experts,

The customer is using the DRV8301DCA in an ESC and needs to be able to ensure that the ESC does not engage the motors on startup, and he is required to have a safety override to ensure it cannot be accidentally controlled when not necessary.

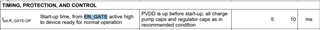

He was thinking that he could use the EN_GATE pin as this control. What happens to the chip if it is held low indefinitely (minutes to hours)? Does this cause any form of damage? Once he drives EN_GATE high again, will the 8301 return to an operational state or does it need a POR at that point?

Let me restate them:

1.) "What happens to the chip if it is held low indefinitely (minutes to hours)?"

2.) "Does this cause any form of damage?"

3.) "Once I drive EN_GATE high again, will the 8301 return to the operational state or does it need a POR at that point?"

4.) "Also, does holding EN_GATE low shut off the buck converter or affect it in any way?"

We hope to receive your confirmation/advise. Thank you.

Best regards,

Gerald