Hi team,

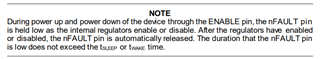

when our customer control this device by ENABLE L:disable to H:Enable, after this device enable, nFAULT level keep L

for 0.4ms.

In datasheet figure 43 or 44, it seems nFAULT keep H for 0.4ms when ENABLE H to L.

Is this the same reason?

And it is said that this reason is come from charge pomp and digital core start-up in this article.:https://e2e.ti.com/support/motor-drivers-group/motor-drivers/f/motor-drivers-forum/942458/drv8320-nfault-behavior-with-enable-pin-and-behavior-after-undervoltage-fault?tisearch=e2e-sitesearch&keymatch=drv8320#

Is this same?

Best regards,

teritama