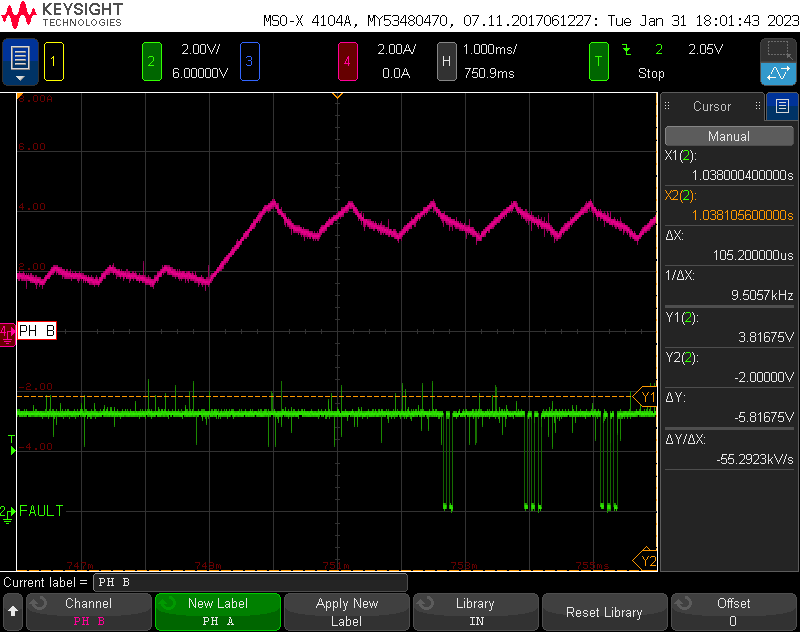

Hello, we are currently troubleshooting our DRV8412 design because we are experiencing latching shutdowns while driving a stepper motor at currents of greater than 3A.

I believe we have eliminated undervoltage protection as the reason for shutdown by probing GVDD during FAULT conditions. There is no significant droop on our 12V GVDD supply (approaching 8.5V UVP threshold) at the time that FAULT is asserted, and we have further reduced this risk by including additional local decoupling at the DRV8412 GVDD pins. Also, we have found that the OTW pin remains HIGH during FAULT conditions.

Therefore, I believe we are experiencing an overcurrent shutdown (Level 2).

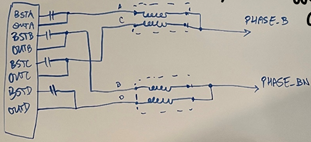

Below is our design using individual DRV8412 parts to drive each phase of a stepper motor. We are using paralleled outputs to increase the current drive capability of the design.

Please note that since we have started troubleshooting, we have modified the above schematic design with the following:

- C419-C422, C441-C444 with 2.2uF capacitors

- R351 & R391 with 27kΩ resistors (OC threshold = 9.7A)

Even though the currents passing through the windings (~3A RMS) are not close to the OC threshold (9.7A), we thought it possible that some current was shooting through the low-resistance paths directly between OUT_A & OUT_C, and OUT_B & OUT_D on each DRV8412.

To test a fix for this, we altered the output inductor configuration to match Figure 15 from the DRV8412 datasheet, in line with the recommendation in Section 9.4.5. This is summarized in the diagram below.

Doing so led to slightly less frequent FAULT conditions from OC latching shutdown when running at over 3A RMS, but these failures would still occur. We also tried placing the DRV8412 into Mode 3 for Parallel Full-Bridge outputs (which required reworks on both input PWM and output drive configurations), but did not see a noticeable difference between the functionality of the design or frequency of FAULT conditions.

Also, it may be important to note that the output filter we are using is the common mode filter SBP-5001T.

Can you please review our design and implemented reworks to suggest possible tests and fixes for our operation?

Thank you.