Hello Ti,

I have a question about of the layout from Gate-Traces. I’ve found a rough estimation formula to calculate the inductance of broad- and edge-coupled traces:

It’s clearly to see that the inductance of the broad coupled (option 2) traces are much smaller. But I’ve never seen a PCB layout that uses broad coupled traces, why is this so?

The only reason I can think of would be that the gate traces are so short that it doesn’t make a huge difference. But with longer traces (a few centimeters) that would make a difference.

The other reason I can think of would be that it's very impractical to route the gate trace in broad coupled form because for example in this layout below, I need the top and bottom layer as power planes (PVDD, GND) (and other things). I think I can’t put a power layer in an inner layer because of the heat distribution.

Are these the reasons or are there other things to consider?

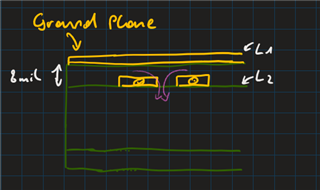

What would happen to the inductance of the gate traces, when they are for example on layer2 and on the top layer is a ground plane? (like in the picture below) If it is changing the inductance, is there then a difference for the low-side and high-side fet gate traces?

Do you know a book where something like this is discussed?

Thanks in advance,

Daniel