Hi TI team,

Test environment: Use the DRV8908-Q1EVM development board and DRV89xx-Q1 configuration panel with 12V power supply.

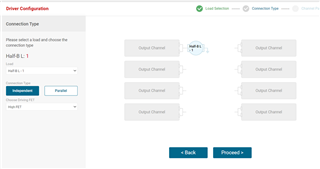

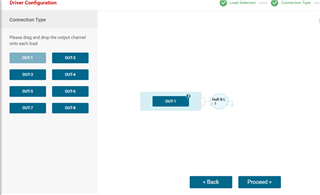

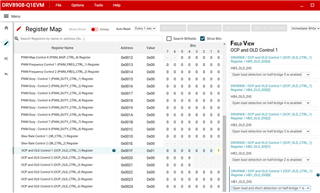

Test steps: Configure DRV89xx-Q1 with OUT1 as the output port, turn off OUT1 open circuit diagnostics, and set the frequency to 80HZ/100HZ/200HZ/2000HZ with OUT1 as the high-side driver as PWM output, and set the duty cycle to 5%/50%/95%, the configuration steps are as follows:

The following table shows the set values and actual test values:

|

Freq. Duty |

80HZ |

100HZ |

200HZ |

2000HZ |

|

5% |

87.25HZ/4.88% |

104.67HZ/4.82% |

209.25HZ/4.61% |

No any waveform |

|

50% |

87.2HZ/49.4% |

104.66HZ/49.36% |

209.30HZ/49.1% |

2093HZ/44.91% |

|

95% |

87.2HZ/94.3% |

104.67HZ/94.27% |

209.27HZ/94.01% |

No any waveform |

It can be seen that there is a large gap between the actual test value and the set value, so my question is why this problem occurs and how to solve it? Many thanks!