Other Parts Discussed in Thread: DRV8353

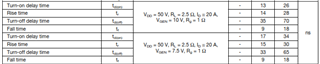

Using a DRV8353RS, I can spin a BLDC motor in FOC mode. This is a custom layout but, follows the recommended layout seen in the datasheet.

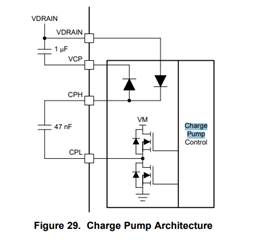

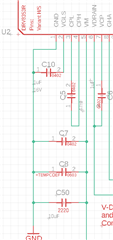

This is a dual supply setup so VM and Vdrain are not directly connected but, both are 15V

I have 3x boards that have failed in the same way where the DRV8353RS chip gets into a permanant failure mode.

Nothing appears wrong from the outside, I can communicate to the TI chip still, I can turn it on and off and at startup I have the following error codes on Register 0 and 1:

0:0480

1: 0040

now, I can clear the register 0: 0400 error code but, the 0080 on reg0 and the 0040 on reg 1 remain no matter what.

The TI chip will then take an extra 110mA @15V on the VM supply and heat itself up to ~50C

This happens when VM and Vdrain are connected to separate 15V (common grounds though). (Connecting to a common 15V also causes the same issue but it is immediate)

with the Vdrain pin floating and the Vm pin connected to 15V, I can still communicate as expected and the chip does not heat itself up or pull the extra 110mA.

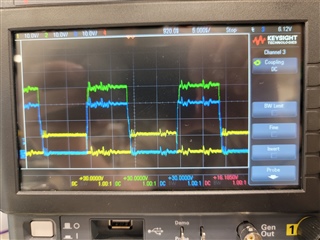

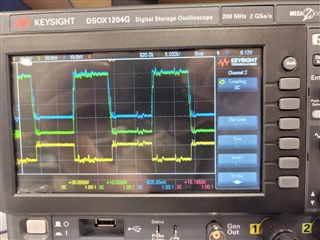

So something is broken on the Gate driving side, I am just trying to understand what could be breaking internally or if the DRV8353RS locked itself into a mode that I can get it out of.

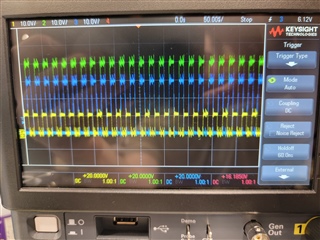

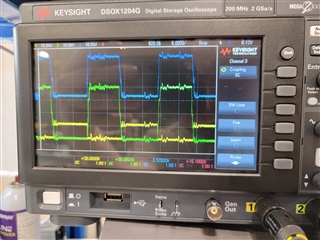

We are fairly early in our programming of the motor but can get a BLDC spinning in trapezoidal (not ideal) or FOC control schemes so I had assumed this was just due to our PWM not having the correct deadtime but, the DRV8353RS handles this by default.

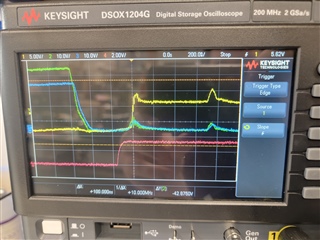

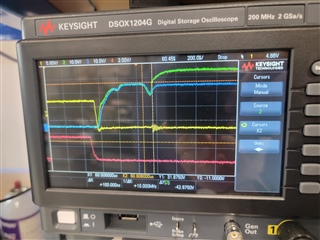

this issue appears to happen when increasing voltage while the motor is spinning or, by increasing RPM while above 50V.