Other Parts Discussed in Thread: DRV8908-Q1, , LP-MSPM0G3507

Hi Team,

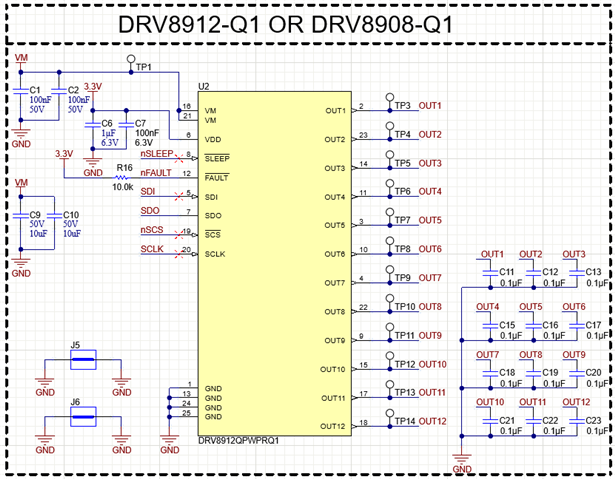

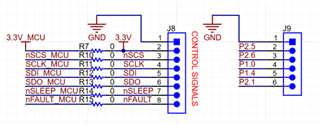

I'm working on building up a SPI driver for communicating with this EVM, however am running into issues & struggling to debug. I have taken a stock EVM, and depopulated resistors R10, R11, R12, and R13 shown below to separate the DRV8908-Q1 from the on-board MCU.

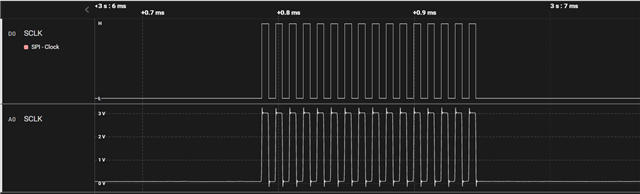

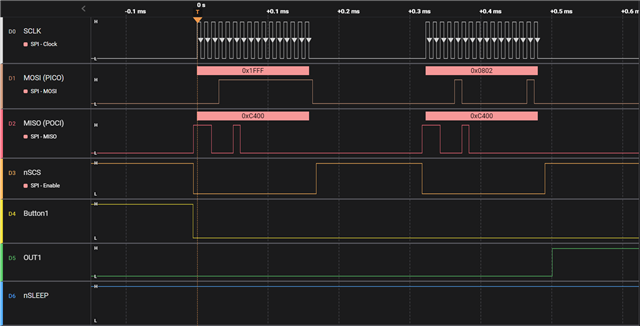

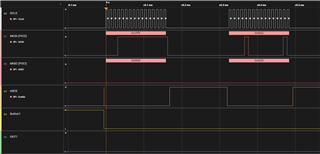

I then perform two SPI writes to the device, one which disables open load diagnostics for all the channels, and one which should set the HB1_HS_EN bit high. See below for a Saleae plot showing the transaction. Unfortunately I am not seeing the OUT1 signal come high as I would expect based on this transaction.

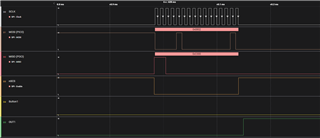

When I use an unmodified, Stock EVM with the GUI, once again taking care to disable the OLD diagnostics, I see the below transaction for triggering HB1_HS_EN. As you can see, this does in fact make OUT1 high as expected.

Can someone help me understand where I might be going wrong, and why I'm not seeing a response on the MISO line for my MSPM0 driver?

Thanks!

- Andy