Dears,

Customer will use the DRV8718 with Domain controller.Now they Want to know the following questions,pls kindly help to check it.

1. This chip driver can control 8 half-bridges (4 H-bridges) and can also be used as a high-edge driver. Can the functions of both H-bridge control and high-edge pre-drive be realized at the same time? (If so, can you provide corresponding application cases?)

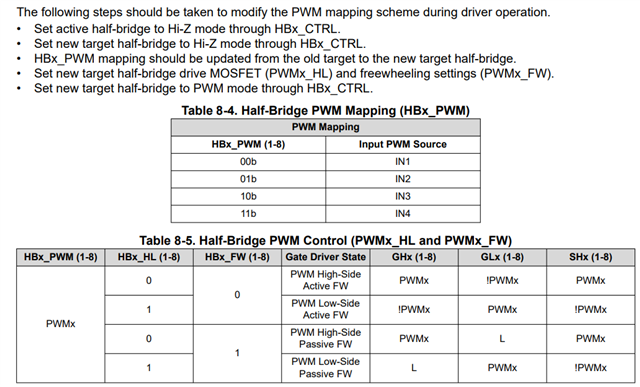

2. Do IN1 to IN4 control feet correspond only to HB1 to HB4 channels?Such as IN1 to HB2?

3. Is there a priority relationship between IN1~IN4 control pin and SPI control?

Thanks