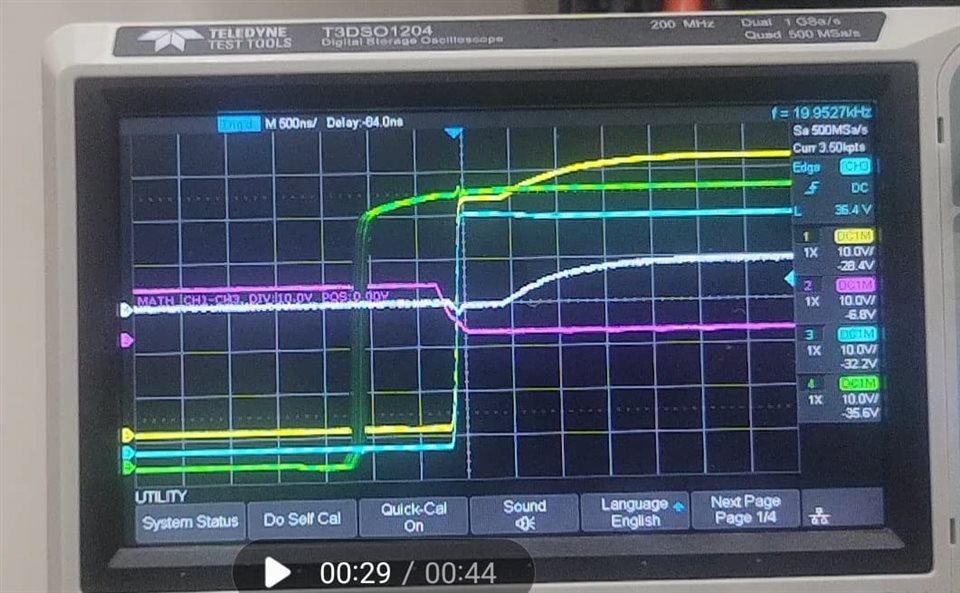

Hi, using the 6x PWM mode, we are observing dead times between high side and low side switching that seem to completely ignore the Tdrive and Tdead settings. Can you help me understand why this is the case? I get the impression that in 6x mode, the VINHx and VINLx determine the state of the gate drives directly, and that only the Idrive setting is meaningful - this is what our traces suggest. However the datasheet for the chip is not clear to us on this subject.

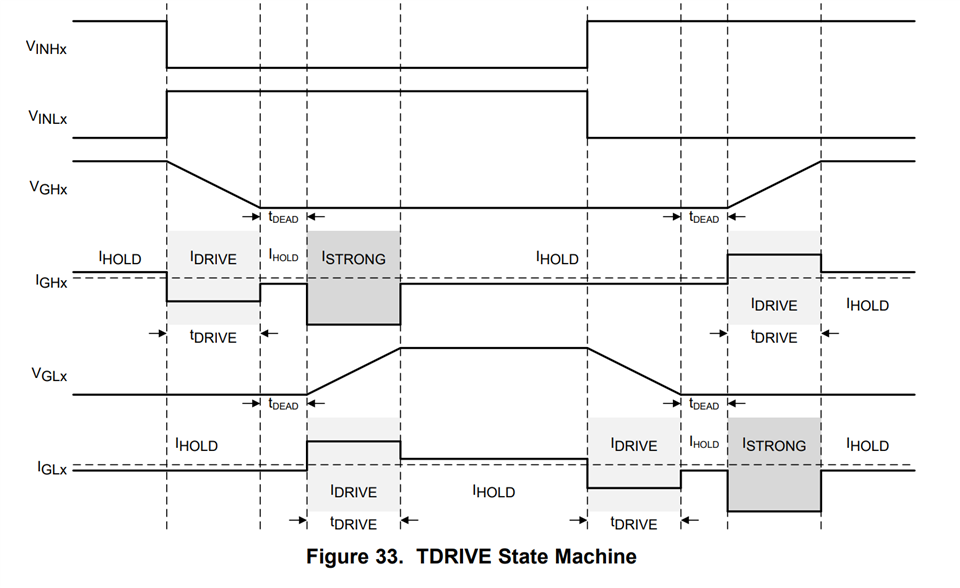

Does the 3X PWM mode behave differently? The timing diagrams we found in the datasheet for our exact chip (DRV8353) suggest yes. The low side gate's state being determined by the VINHx input + Tdrive + Tdead makes sense.

Your help gaining clarity would be much appreciated.

-S

The hs waits 400ns before turning on,

The hs waits 400ns before turning on,