Part Number: DRV8243S-Q1LEVM

Hi,

Our customer encountered some issues while debugging the BDC driver chip DRV8243S, as follows:

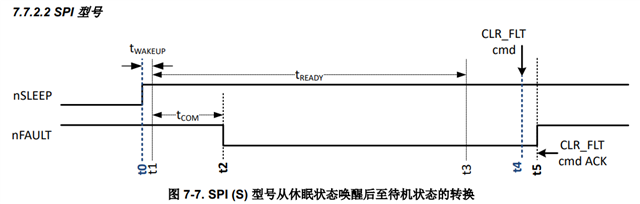

When attempting to switch the driver chip from sleep mode to standby mode, raise the nSleep pin and send CLR_ FLT cmd after detecting that the nFault pin is pulled low, nFault pin cannot be raised again and cannot enter standby mode.

Read Fault_SUMMARY Register When the register reads 0 * 60 and POR and nFault are set to 1.

May I ask what may be the cause of this, and do we need additional operation to enter standby mode?

Timing chart for switching from sleep to standby mode:

Thank you!