Hello,

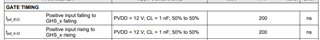

I have a question regarding the gate timing of the DRV8305. In your Datasheed (Revised February 2016) in the electrical characteristics table under Gate timing (page 10) there're two parameters named t_pd_If-O and t_pd_Ir-O which are described by "Positive input rising/falling to GHS_x rising/falling".

I have measured the device with an oscilloscope trying to figure out the timing and can't really figure out where these time parameters show up. So I have 2 questions:

- What does "Positive Input" mean? Is that INH_x?

2. Could this parameter be the time between INH_x rising/falling and the low side gate GLS_x rising/falling?