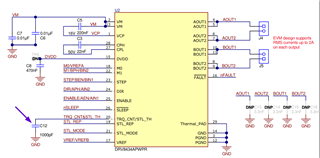

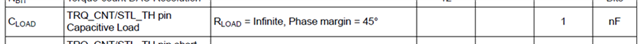

The stepper driver DRV8434A should be operated in "stall threshold" mode, i.e. STL_MODE = 1, STL_TH = input. For maximum flexibility , I would like to have the threshold voltage generated by the FPGA via a PWM - for this, the largest possible capacitance at the STL_TH pin would be an advantage. However, the data sheet states:

Does this limit of up to 1nF also apply in stall threshold mode, where the pin is an input?

Thanks and bye

Hanno