Other Parts Discussed in Thread: DRV8329, CSD19506KTT, UCC27284, , C2000WARE

Hi Team,

The half-bridge gate driver replaces the DRV8329+CSD19506KTT with 3 UCC27284 to control the BLDC and there're 2 issues may need your help:

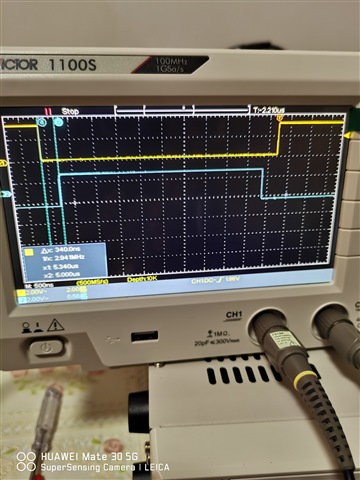

1) Configure PWM in hal.c, EPWM3 has no waveforms, while the other two phases have PWM waves:

// GPIO227->EPWM3A->M1_UH

GPIO_setPinConfig(GPIO_227_EPWM3_A);

GPIO_setDirectionMode(227, GPIO_DIR_MODE_OUT);

GPIO_setPadConfig(227, GPIO_PIN_TYPE_STD);

// GPIO230->EPWM3B->M1_UL

GPIO_setPinConfig(GPIO_230_EPWM3_B);

GPIO_setDirectionMode(230, GPIO_DIR_MODE_OUT);

GPIO_setPadConfig(230, GPIO_PIN_TYPE_STD);

// GPIO0->EPWM1A->M1_VH

GPIO_setPinConfig(GPIO_0_EPWM1_A);

GPIO_setDirectionMode(0, GPIO_DIR_MODE_OUT);

GPIO_setPadConfig(0, GPIO_PIN_TYPE_STD);

// GPIO1->EPWM1B->M1_VL

GPIO_setPinConfig(GPIO_1_EPWM1_B);

GPIO_setDirectionMode(1, GPIO_DIR_MODE_OUT);

GPIO_setPadConfig(1, GPIO_PIN_TYPE_STD);

// GPIO2->EPWM2_A->M1_WH

GPIO_setPinConfig(GPIO_2_EPWM2_A);

GPIO_setDirectionMode(2, GPIO_DIR_MODE_OUT);

GPIO_setPadConfig(2, GPIO_PIN_TYPE_STD);

// GPIO3->EPWM2_B->M1_WL

GPIO_setPinConfig(GPIO_3_EPWM2_B);

GPIO_setDirectionMode(3, GPIO_DIR_MODE_OUT);

GPIO_setPadConfig(3, GPIO_PIN_TYPE_STD);

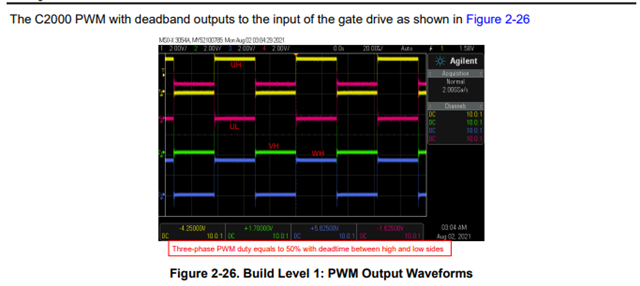

2) Refer to DRV8329AEVM control flow for UCC27284 with non-SPI interface. Could you help share how to port the software and is there any reference documentation available? The software is based on the C2000\C2000Ware_MotorControl_SDK_4_02_01_00\solutions\universal_motorcontrol_lab\f280013x project.

Could you help check this case? Thanks.

Best Regards,

Cherry